Preliminary W49F201

128K

◊

16 CMOS FLASH MEMORY

Publication Release Date: June 1999

- 1 -

Revision A1

GENERAL DESCRIPTION

The W49F201 is a 2-megabit, 5-volt only CMOS flash memory organized as 128K

◊

16 bits. The

device can be programmed and erased in-system with a standard 5V power supply. A 12-volt V

PP

is

not required. The unique cell architecture of the W49F201 results in fast program/erase operations

with extremely low current consumption (compared to other comparable 5-volt flash memory

products). The device can also be programmed and erased using standard EPROM programmers.

FEATURES

∑

Single 5-volt operations:

-

5-volt Read/Erase/Program

∑

Fast Program operation:

-

Word-by-Word programming: 50

µ

S (max.)

∑

Fast Erase operation: 60 mS (typ.)

∑

Fast Read access time: 45/55 nS

∑

Endurance: 1K/10K cycles (typ.)

∑

Ten-year data retention

∑

Hardware data protection

∑

Sector configuration

-

One 8K words boot block with lockout

protection

-

Two 8K words parameter blocks

-

One 104K words (208K bytes) Main Memory

Array Blocks

∑

Low power consumption

-

Active current: 25 mA (typ.)

-

Standby current: 20

µ

A (typ.)

∑

Automatic program and erase timing with

internal V

PP

generation

∑

End of program or erase detection

-

Toggle bit

-

Data polling

∑

Latched address and data

∑

TTL compatible I/O

∑

JEDEC standard word-wide pinouts

∑

Available packages: 44-pin SOP, 48-pin TSOP

Preliminary W49F201

- 2 -

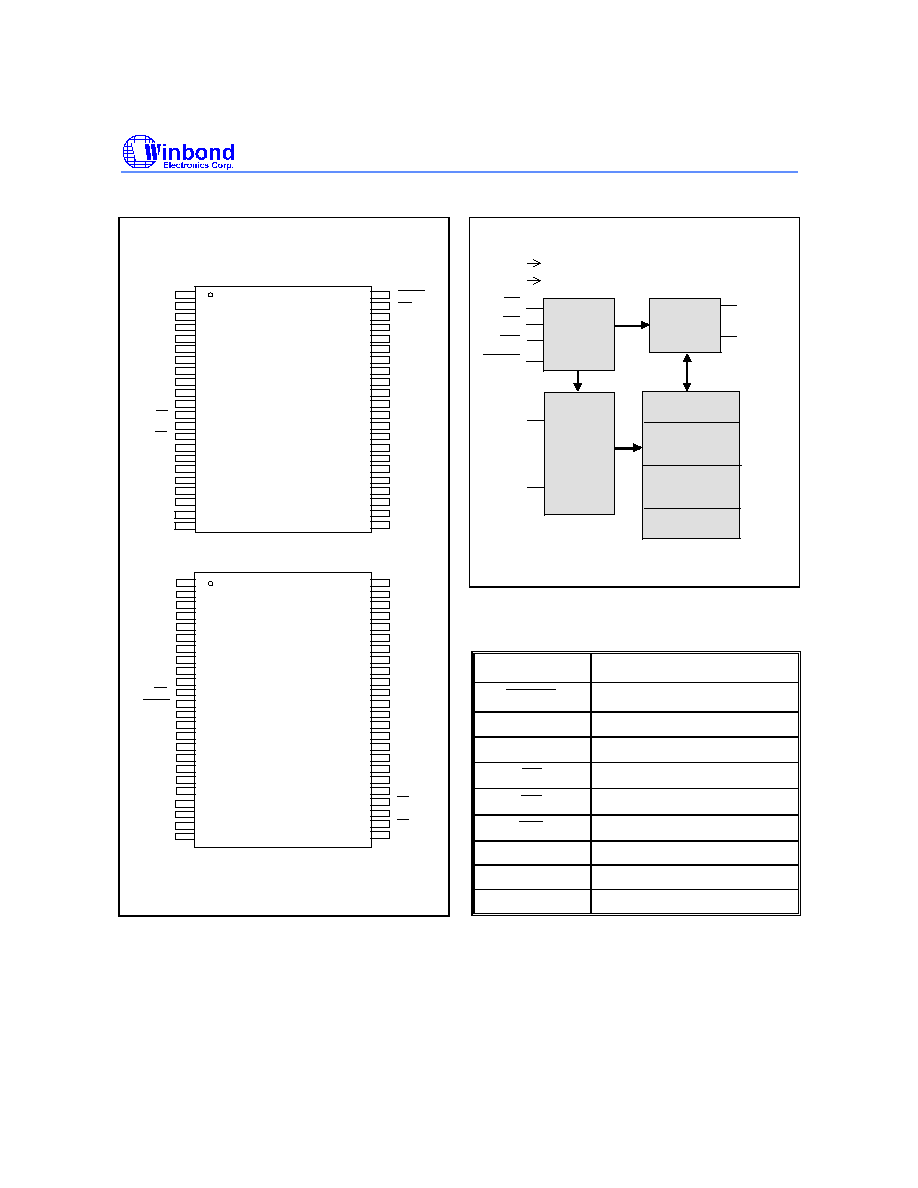

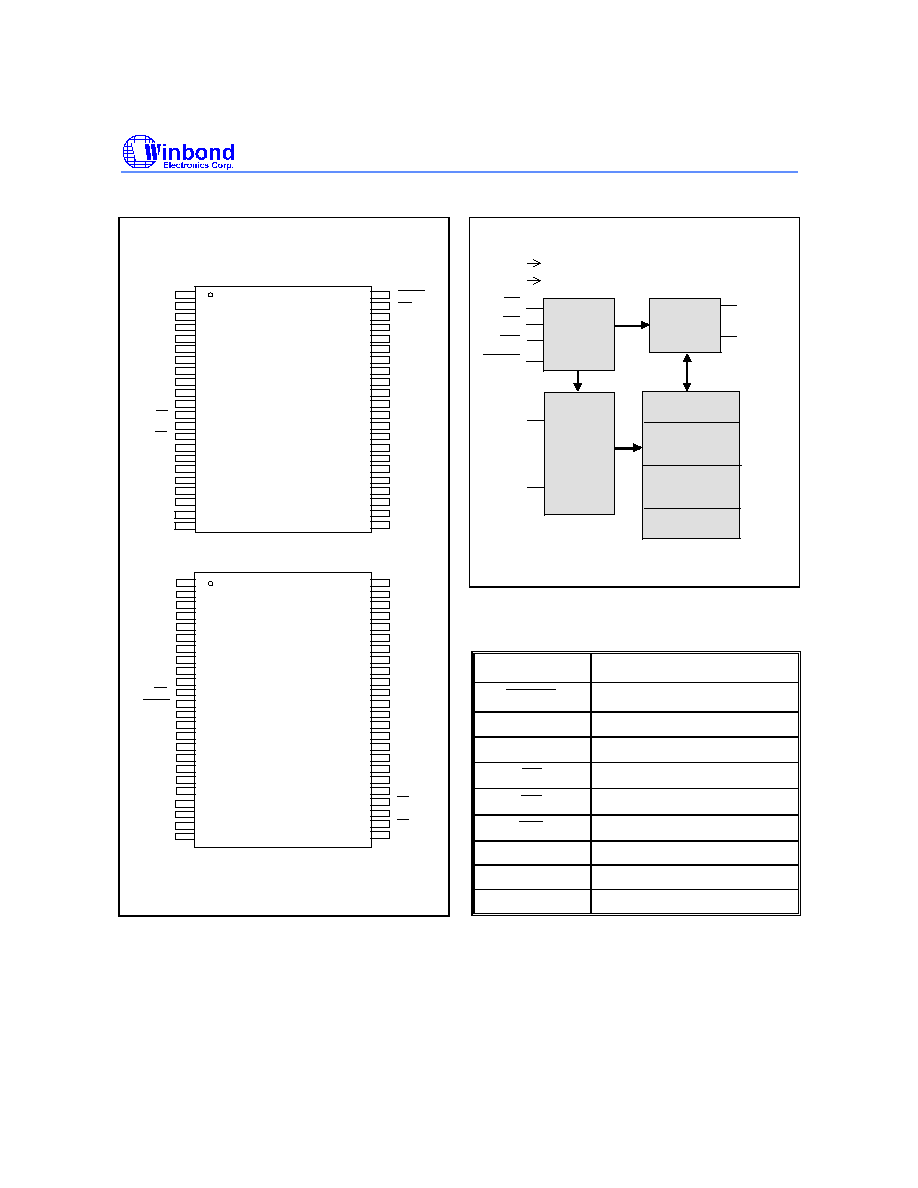

PIN CONFIGURATIONS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

DQ15

A9

A10

A11

A12

A13

A14

A15

OE

GND

48-pin

TSOP

24

23

NC

A16

WE

CE

A7

A6

A5

A4

A3

A2

A1

A0

21

22

48

47

7

46

45

44

43

42

41

NC

NC

NC

NC

RESET

NC

NC

A8

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

V

CC

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

GND

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

DQ15

GND

OE

44-pin

SOP

24

23

A16

CE

A0

21

22

40

39

38

37

36

35

34

33

32

31

30

29

28

27

44

43

42

41

NC

A7

A6

A5

A4

A3

A2

A1

NC

NC

A9

A10

A11

A12

A13

A14

A15

WE

RESET

A8

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

V

CC

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

GND

NC

26

25

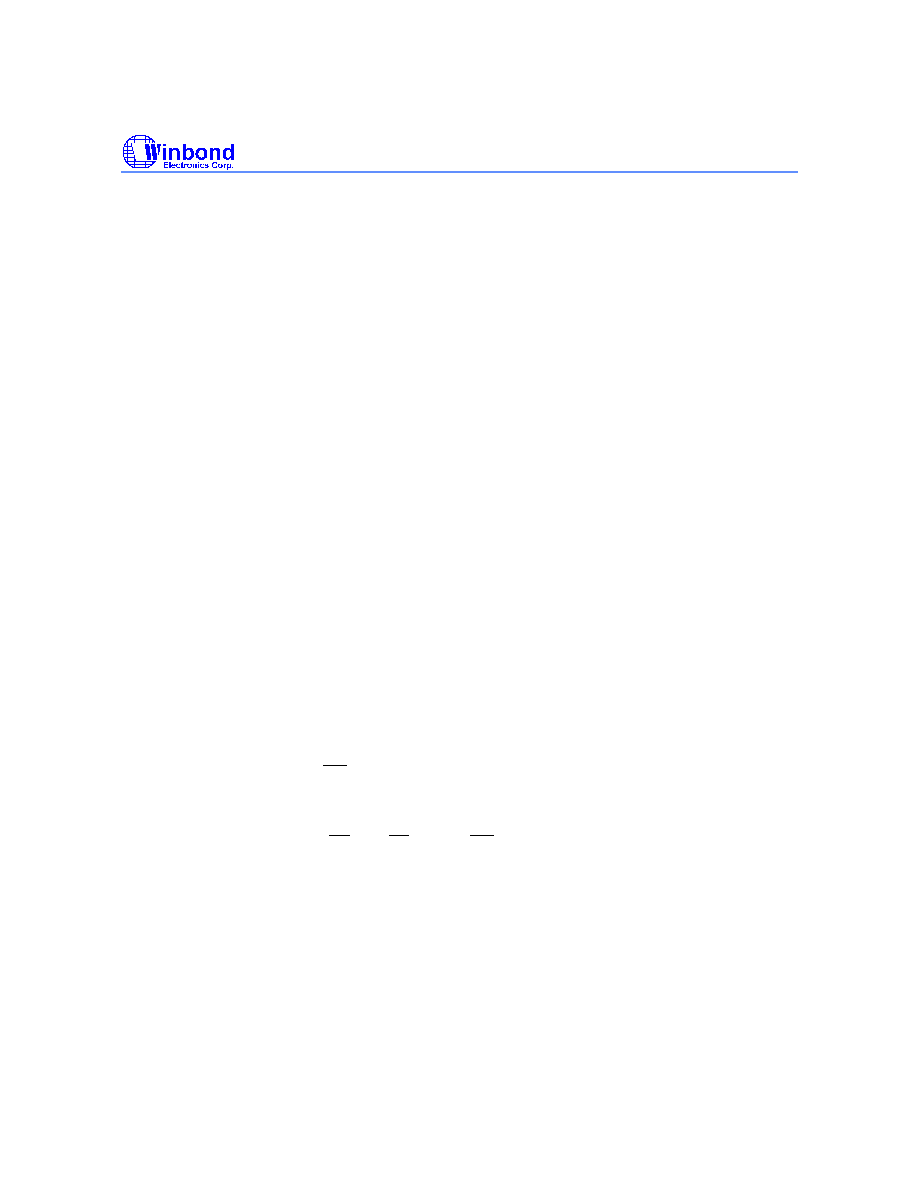

BLOCK DIAGRAM

CONTROL

OUTPUT

BUFFER

DECODER

MAIN MEMORY

104K WORDS

CE

OE

WE

A0

.

.

A16

.

.

DQ0

DQ15

V

DD

V

SS

BOOT BLOCK

8K WORDS

PARAMETER

BLOCK2

8K WORDS

PARAMETER

BLOCK1

8K WORDS

1FFFF

06000

05FFF

04000

03FFF

02000

01FFF

00000

RESET

PIN DESCRIPTION

SYMBOL

PIN NAME

RESET

Reset

A0

-

A16

Address Inputs

DQ0

-

DQ15

Data Inputs/Outputs

CE

Chip Enable

OE

Output Enable

WE

Write Enable

V

DD

Power Supply

GND

Ground

NC

No Connection

Preliminary W49F201

Publication Release Date: June 1999

- 3 -

Revision A1

FUNCTIONAL DESCRIPTION

Read Mode

The read operation of the W49F201 is controlled by CE and OE, both of which have to be low for

the host to obtain data from the outputs. CE is used for device selection. When CE is high, the chip

is de-selected and only standby power will be consumed. OE is the output control and is used to gate

data to the output pins. The data bus is in high impedance state when either CE or OE is high. Refer

to the timing waveforms for further details.

Reset Operation

The RESET

input pin can be used in some application. When RESET pin is at high state, the device

is in normal operation mode. When RESET pin is driven low for at least a period of T

RP

, it will halts

the device and all outputs are at high impedance state. The device also resets the internal state

machine to read array data. The operation that was interrupted should be reinitiated once the device

is ready to accept another command sequence to assure data integrity. As the high state re-asserted

to the RESET pin, the device will return to read or standby mode, it depends on the control signals.

The system can read data T

RH

after the RESET

pin returns to V

IH

. The other function for RESET pin

is temporary reset the boot block. By applying the 12V to RESET pin, the boot block can be

reprogrammed even though the boot block lockout function is enabled.

Boot Block Operation

There is one 8K-word boot block in this device, which can be used to store boot code. It is located in

the first 8K words of the memory with the address range from 0000(hex) to 1FFF(hex).

See Command Codes for Boot Block Lockout Enable for the specific code. Once this feature is set

the data for the designated block cannot be erased or programmed (programming lockout); other

memory locations can be changed by the regular programming method.

There is one condition that the lockout feature can be overrides. Just apply 12V to RESET

pin, the

lockout feature will temporary be inactivated and the boot block can be erased/programmed. Once

the RESET pin returns to TTL level, the lockout feature will be activated again.

In order to detect whether the boot block feature is set on the 8K-words block, users can perform

software command sequence: enter the product identification mode (see Command Codes for

Identification/Boot Block Lockout Detection for specific code), and then read from address "0002

hex". If the output data in DQ0 is "1", the boot block programming lockout feature is activated; if the

output data in DQ0 is "0", the lockout feature is inactivated and the block can be

erased/programmed.

To return to normal operation, perform a three-byte command sequence (or an alternate single-word

command) to exit the identification mode. For the specific code, see Command Codes for

Identification/Boot Block Lockout Detection.

Chip Erase Operation

The chip-erase mode can be initiated by a six-word command sequence. After the command loading

cycle, the device enters the internal chip erase mode, which is automatically timed and will be

Preliminary W49F201

- 4 -

completed in a fast 100 mS (typical). The host system is not required to provide any control or timing

during this operation. The entire memory array will be erased to FF(hex). by the chip erase operation

if the boot block programming lockout feature is not activated. Once the boot block lockout feature is

activated, the chip erase function will erase all the sectors except the boot mode.

Sector Erase Operation

The three sectors, main memory and two parameters blocks, can be erased individually by initiating a

six-word command sequence. Sector address is latched on the falling WE edge of the sixth cycle

while the 30(hex) data input command is latched at the rising edge of WE. After the command

loading cycle, the device enters the internal sector erase mode, which is automatically timed and will

be completed in a fast 100 mS (typical). The host system is not required to provide any control or

timing during this operation. The device will automatically return to normal read mode after the erase

operation completed. Data polling and/or Toggle Bits can be used to detect end of erase cycle.

When the boot block lockout feature is inactivated, the boot block and the main memory block will be

erased together. Once the boot block is locked, only the main memory block will be erased by the

execution of sector erase operation.

Program Operation

The W49F201 is programmed on a word-by-word basis. Program operation can only change logical

data "1" to logical data "0" The erase operation (changed entire data in main memory and/or boot

block from "0" to "1" is needed before programming.

The program operation is initiated by a 4-word command cycle (see Command Codes for Word

Programming). The device will internally enter the program operation immediately after the word-

program command is entered. The internal program timer will automatically time-out (50

µ

S max. -

T

BP

) once completed and return to normal read mode. Data polling and/or Toggle Bits can be used to

detect end of program cycle.

Hardware Data Protection

The integrity of the data stored in the W49F201 is also hardware protected in the following ways:

(1) Noise/Glitch Protection: A WE pulse of less than 15 nS in duration will not initiate a write cycle.

(2) V

DD

Power Up/Down Detection: The programming operation is inhibited when V

DD

is less than

2.5V typical.

(3) Write Inhibit Mode: Forcing OE low, CE high, or WE high will inhibit the write operation. This

prevents inadvertent writes during power-up or power-down periods.

(4) V

DD

power-on delay: When V

DD

has reached its sense level, the device will automatically time-out

5 mS before any write (erase/program) operation.

Data Polling (DQ

7

)- Write Status Detection

The W49F201 includes a data polling feature to indicate the end of a program or erase cycle. When

the W49F201 is in the internal program or erase cycle, any attempt to read DQ

7

of the last word

loaded will receive the complement of the true data. Once the program or erase cycle is completed,

DQ

7

will show the true data. Note that DQ

7

will show logical "0" during the erase cycle, and become

logical "1" or true data when the erase cycle has been completed.

Preliminary W49F201

Publication Release Date: June 1999

- 5 -

Revision A1

Toggle Bit (DQ

6

)- Write Status Detection

In addition to data polling, the W49F201 provides another method for determining the end of a

program cycle. During the internal program or erase cycle, any consecutive attempts to read DQ

6

will

produce alternating 0's and 1's. When the program or erase cycle is completed, this toggling between

0's and 1's will stop. The device is then ready for the next operation.

Product Identification

The product ID operation outputs the manufacturer code and device code. Programming equipment

automatically matches the device with its proper erase and programming algorithms.

The manufacturer and device codes can be accessed by software or hardware operation. In the

software access mode, a six-word (or JEDEC 3-word) command sequence can be used to access the

product ID. A read from address 0000H outputs the manufacturer code, 00DA(hex). A read from

address 0001(hex) outputs the device code, 00AE(hex). The product ID operation can be terminated

by a three-word command sequence or an alternative one-word command sequence (see Command

Definition table).

In the hardware access mode, access to the product ID is activated by forcing CE and OE low, WE

high, and raising A9 to 12 volts.

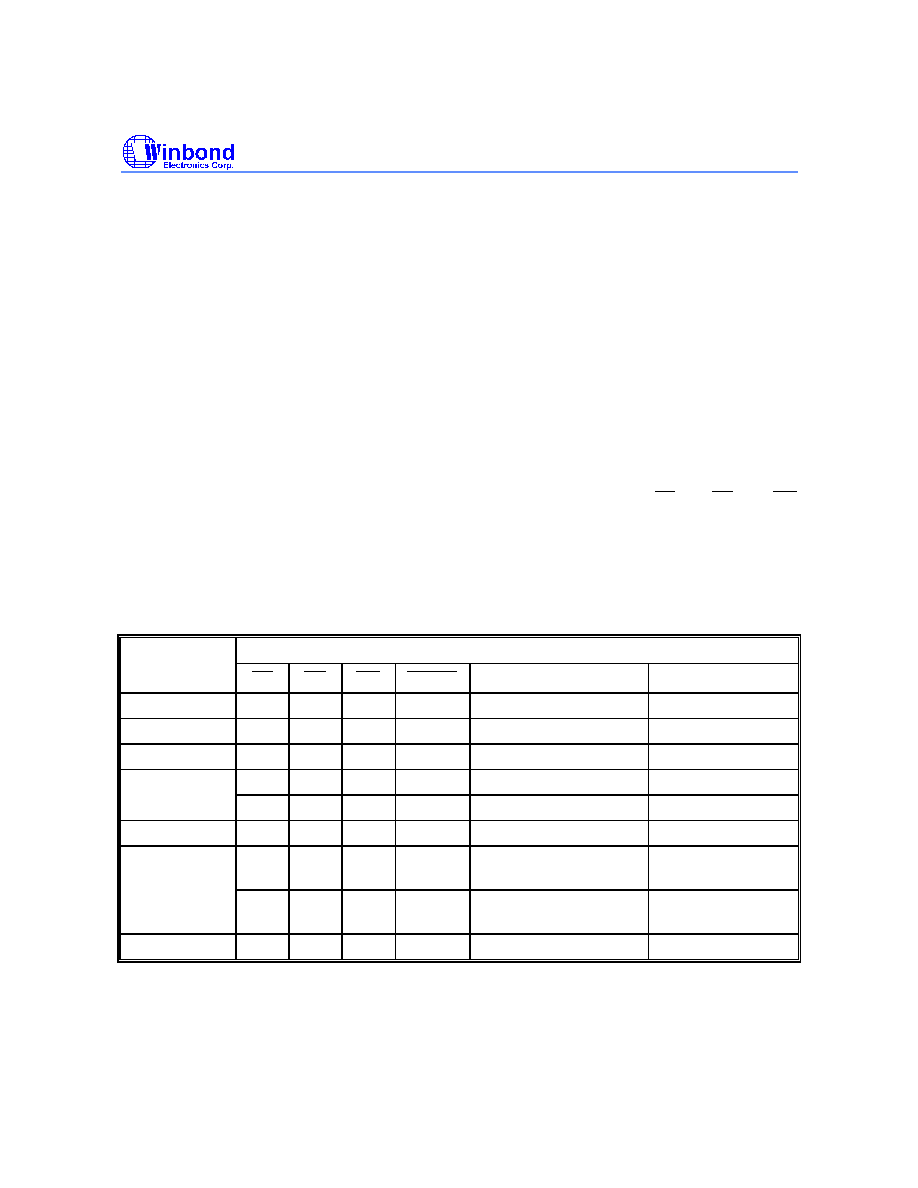

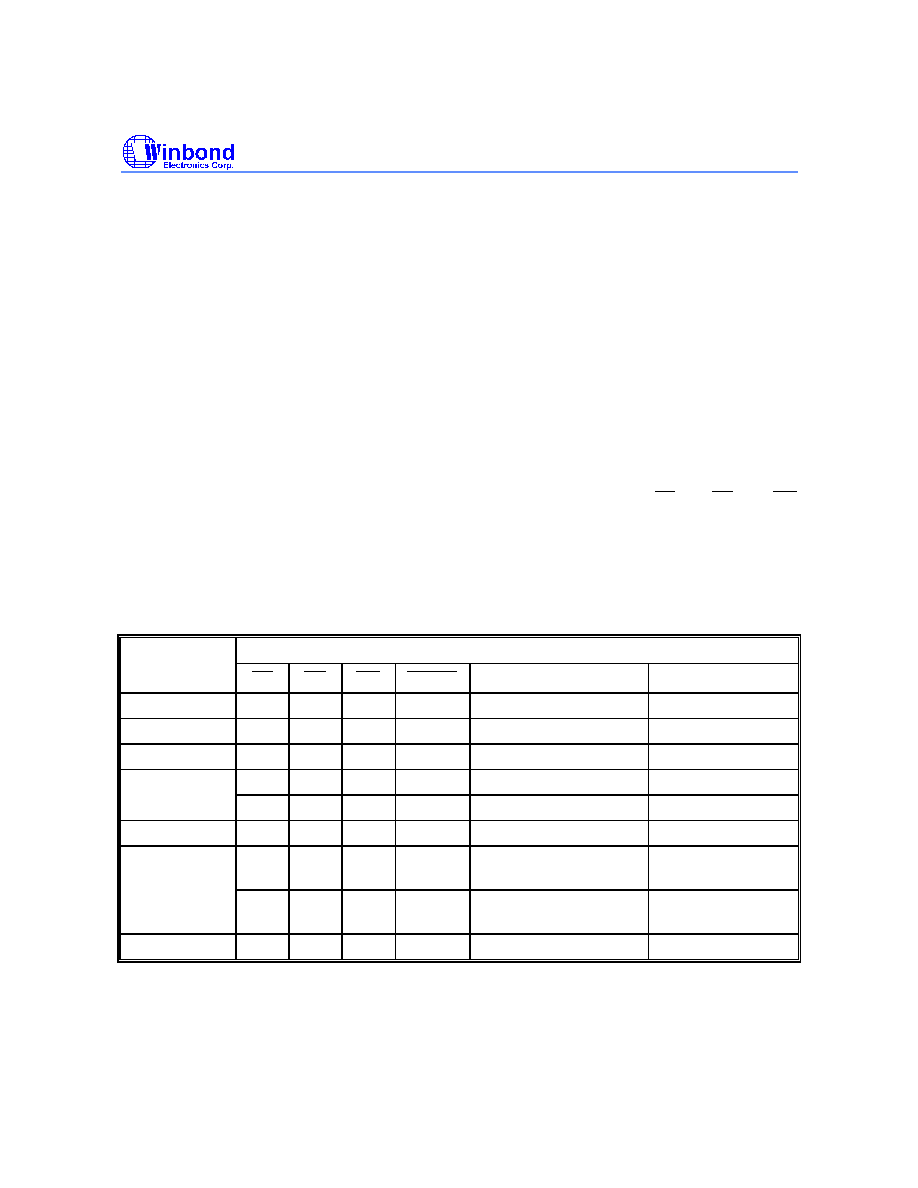

TABLE OF OPERATING MODES

Operating Mode Selection

(V

HH

= 12V

±

5

%

)

MODE

PINS

CE

OE

WE

RESET

ADDRESS

DQ.

Read

V

IL

V

IL

V

IH

V

IH

A

IN

Dout

Erase/Program

V

IL

V

IH

V

IL

V

IH

A

IN

Din

Standby

V

IH

X

X

V

IH

X

High Z

Erase/Program

X

V

IL

X

V

IH

X

High Z/D

OUT

Inhibit

X

X

V

IH

V

IH

X

High Z/D

OUT

Output Disable

X

V

IH

X

V

IH

X

High Z

Product ID

V

IL

V

IL

V

IH

V

IH

A0 = V

IL

;

A1

-

A15 = V

IL

; A9 = V

HH

Manufacturer Code

00DA (Hex)

V

IL

V

IL

V

IH

V

IH

A0 = V

IH

;

A1

-

A15 = V

IL

; A9 = V

HH

Device Code

00AE (Hex)

Reset

X

X

X

V

IL

X

High Z