1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2004-2005, Zarlink Semiconductor Inc. All Rights Reserved.

Features

∑ 4,096 x 2,048 blocking switching between

backplane and local streams

∑ 1,024 x 1,024 non-blocking switching between

local streams

∑ 2,048 x 2,048 non-blocking switching between

backplane streams

∑ Rate conversion between backplane and local

streams

∑ Backplane interface accepts data rates of

8.192 Mbps or 16.384 Mbps

∑ Local interface accepts data rates of 2.048 Mbps,

4.096 Mbps or 8.192 Mbps on a per group basis

∑ Meets all the key H.110 mandatory signal

requirements including timing

∑ Per-channel variable or constant throughput

delay

∑ Per-stream input delay, programmable for local

streams on a per bit basis

∑ Per-stream output advancement, programmable

for backplane and local streams

∑ Per-channel direction control for backplane

streams and local streams

∑ Per-channel message mode for backplane and

local streams

∑ Per-channel high impedance output control for

backplane and local streams

∑ Compatible to Stratum 4 Enhanced clock

switching standard

∑ Integrated PLL conforms to Telcordia GR-1244-

CORE Stratum 4 Enhanced switching standard

- Holdover Mode with holdover frequency stability

of 0.07 ppm

- Jitter attenuation from 1.52 Hz.

- Time interval error (TIE) correction

- Master and Slave mode operation

∑ Non-multiplexed microprocessor interface

∑ Connection memory block-programming for fast

device initialization

∑ Pseudo-Random Binary Sequence (PRBS) pattern

generation and testing for backplane and local

streams

∑ Conforms to the mandatory requirements of the

IEEE-1149.1 (JTAG) standard

∑ 3.3 V operation with 5 V tolerant inputs and I/O's

∑ 5 V tolerant PCI driver on CT-Bus I/O's

Applications

∑ Carrier-grade VoIP Gateways

∑ IP-PBX and PABX

∑ Intregrated Access Devices

∑ Access Servers

∑ CTI Applications/CompactPCI

Æ

Platforms

∑ H.110, H.100, ST-BUS and proprietary Backplane

Applications

Description

The ZL50030 Digital Switch provides switching

capacities of 4,096 x 2,048 channels between

backplane and local streams, 1,024 x 1,024 channels

among local streams, and 2,048 x 2,048 channels

among backplane streams. The local connected serial

inputs and outputs have 32, 64 and 128 64 kbps

channels per frame with data rates of 2.048, 4.096 and

8.192 Mbps respectively. The backplane connected

serial inputs and outputs have 128 and 256 64 kbps

channels per frame with data rates of 8.192 and

16.384 Mbps respectively.

The device has features that are programmable on a

per-stream or a per-channel basis including message

mode, input delay offset, output advancement offset,

and direction control.

February 2005

Ordering Information

ZL50030GAC

220 Ball - PBGA

-40

∞C to +85∞C

ZL50030

Flexible 4 K x 2 K Channel Digital Switch with

H.110 Interface and 1 K x 1 K Local Switch

Data Sheet

Zarlink Semiconductor US Patent No. 5,602,884, UK Patent No. 0772912,

France Brevete S.G.D.G. 0772912; Germany DBP No. 69502724.7-08

ZL50030

Data Sheet

3

Zarlink Semiconductor Inc.

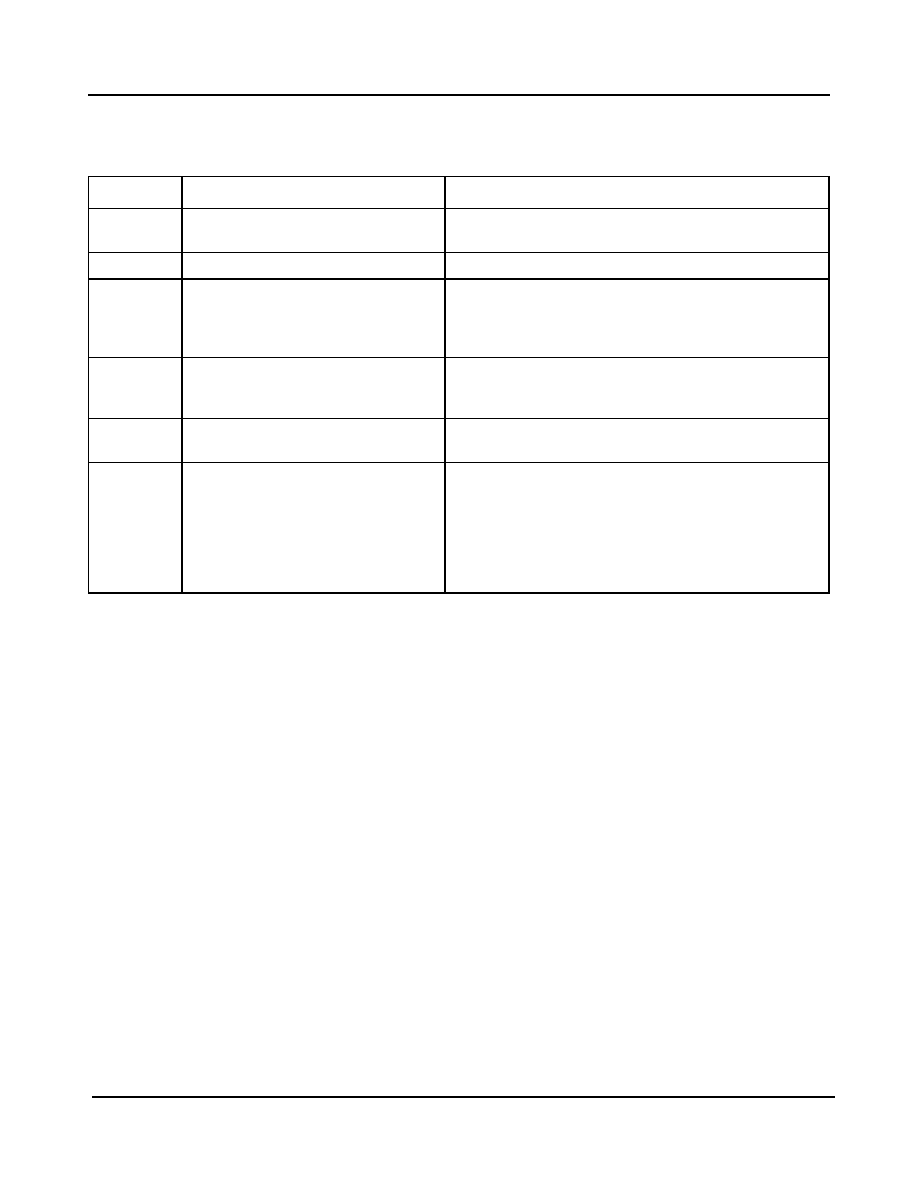

Changes Summary

The following table captures the changes from the March 2004 issue.

Page

Item

Change

27, 47

Section 17.2 and Table 20

Added description clarifying that the MTIE reset must be

set when the device is in the slave mode.

49

Table 21

Added MRST (bit 10) in Mode Selection table.

29, 30

Section 17.7 and Section 18.1

Deleted the intrinsic jitter descriptions in Section 17.7

and Section18.1, and replaced them with Table "AC

Electrical Characteristics - Output Clock Jitter

Generation (Unfiltered).

57

"AC Electrical Characteristics -

Output Frame Pulse and Output

Clock Timing"

The parameter Delta,

, is replaced by actual numbers

in all tables.

56

"AC Electrical Characteristics - Input

Frame Pulse and Input Clock Timing"

The Phase Correction,

, is replaced by actual numbers.

65, 67

"AC Electrical Characteristics -

Backplane Serial Streams with Data

Rate of 8 Mbps", "AC Electrical

Characteristics - Backplane Serial

Streams with Data Rate of 16 Mbps"

and "AC Electrical Characteristics -

Local Serial Stream Input Timing"

Input data sampling timings were updated for clarity

purposes.

ZL50030

Data Sheet

5

Zarlink Semiconductor Inc.

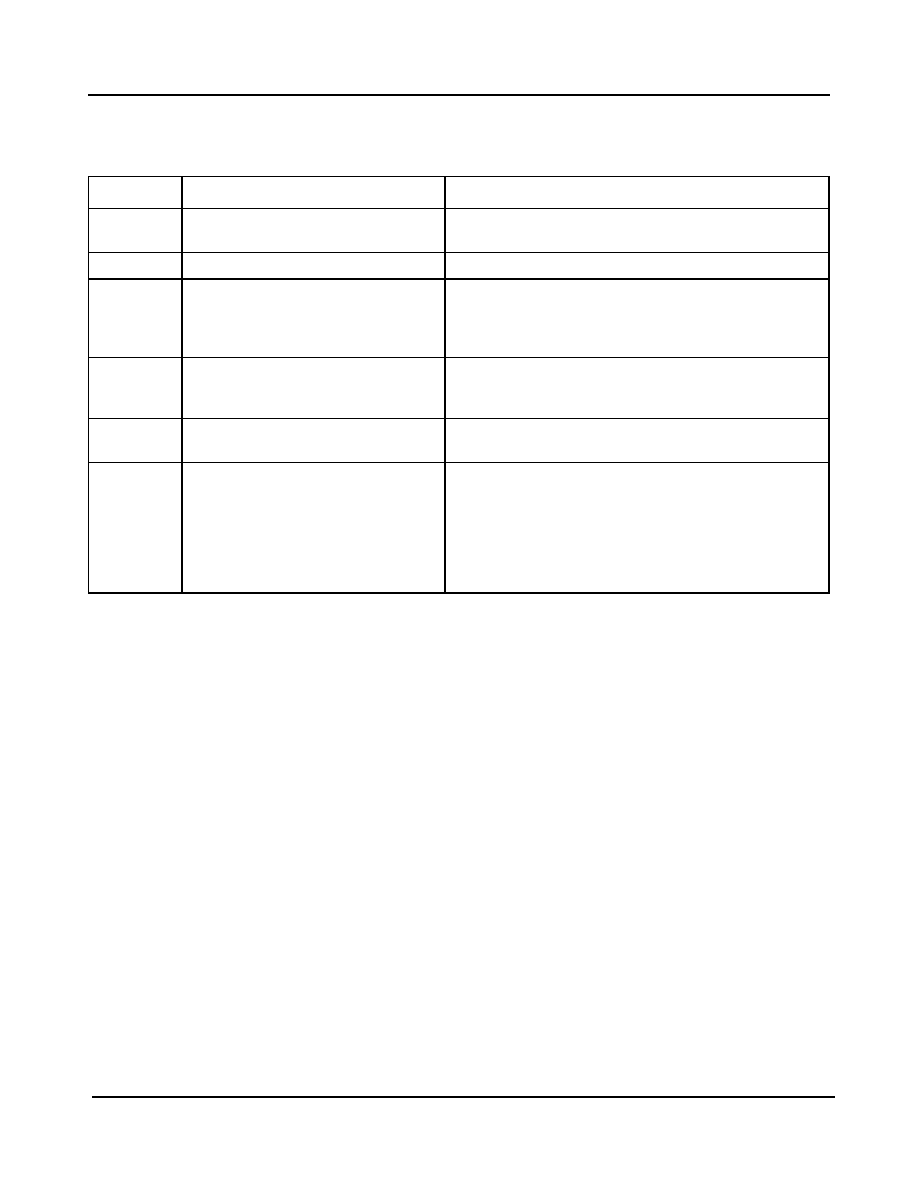

Pin Description

PBGA

Ball Number

Name

Description

E7, E8, E9, E10,

E11, E12, F6,

F11, F12, G12,

H5, H12, J5, J12,

K5, K12, L5, L6,

L7, L10, L11, L12,

M5, M12

V

DD

+3.3 Volt Power Supply

E5, E6, F5, G5

V

DD5V

+5.0 V/+3.3 V Power Supply. If 5 V power supply is tied to these pins,

BSTio0-31 pins will meet 5 V PCI requirements. If 3.3 V power supply is tied

to these pins, BSTio0-31 pins will meet 3.3 V PCI requirements.

F7, F8, F9, F10,

G6, G7, G8, G9,

G10, G11, H6, H7,

H8, H9, H10, H11,

J6, J7, J8, J9,

J10, J11, K6, K7,

K8, K9, K10, K11,

L8

V

SS

Ground

M10

V

DD_APLL

+3.3 Volt Analog PLL Power Supply. No special filtering is required for this

pin.

L9

V

SS_APLL

Analog PLL Ground

P6

RESET

Device Reset (5 V Tolerant Input). This input (active low) puts the device in

its reset state; this state clears the device's internal counters and registers.

To ensure proper reset action, the reset pin must be low for longer than

400ns. To ensure proper operation, a delay of 100

µs must be applied before

the first microprocessor access is performed after the RESET pin is set high.

The device reset also tristates LSTio0-15 and BSTio0-31. When in a RESET

condition, the C8_A_io, FRAME_A_io, C8_B_io, and FRAME_B_io signals

are tri-stated.

F1, E1, D1, C1,

B1, A1, F2, F3,

E3, E2, D2, C2,

B2, A2, C3, D3

BSTio0-15

Backplane Serial Input/Output Streams 0 - 15 (5 V Tolerant PCI I/Os).

In H.110 mode, these pins accept or output (selectable on a per channel

basis) serial TDM data streams at 8.192 Mbps with 128 channels per

stream. In the 16 Mbps mode, these pins accept or output serial TDM data

streams at 16.384 Mbps with 256 channels per stream.

B3, A3, B4, A4,

B5, B6, A5, A6,

B7, A7, A8, B8,

A9, A10, B9, B10

BSTio16 - 31 Backplane Serial Input/Output Streams 16 - 31 (5 V Tolerant PCI I/Os).

In H.110 mode, these pins accept or output (selectable on a per channel

basis) serial TDM data streams at 8.192 Mbps with 128 channels per

stream. In the 16 Mbps mode, these pins are tristated internally and should

be connected to ground.

A11, A12, A13,

A14

LSTio0-3

Group 0 Local Serial Bi-directional Streams 0 - 3 (5 V Tolerant I/Os).

In 2 Mbps, 4 Mbps or 8 Mbps mode, these pins accept or output (selectable

on a per channel basis) data rates of 2.048, 4.096 or 8.192 Mbps with 32, 64

or 128 channels per stream respectively.