# **CMOS 4-BIT SINGLE CHIP MICROCOMPUTER** S1C621A0 Technical Manual S1C621A0 Technical Hardware/S1C621A0 Technical Software

#### **PREFACE**

This manual is individualy described about the hardware and the software of the S1C621A0.

# I. S1C621A0 Technical Hardware

This part explains the function of the S1C621A0, the circuit configurations, and details the controlling method.

# II. S1C621A0 Technical Software

This part explains the programming method of the S1C621A0.

#### The information of the product number change

Starting April 1, 2001, the product number will be changed as listed below. To order from April 1, 2001 please use the new product number. For further information, please contact Epson sales representative.

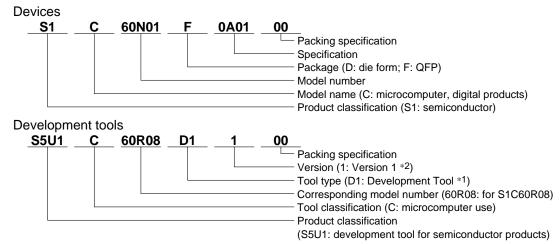

#### Configuration of product number

<sup>\*1:</sup> For details about tool types, see the tables below. (In some manuals, tool types are represented by one digit.)

#### Comparison table between new and previous number

S1C60 Family processors

| <u> </u>     | ·        |

|--------------|----------|

| Previous No. | New No.  |

| E0C6001      | S1C60N01 |

| E0C6002      | S1C60N02 |

| E0C6003      | S1C60N03 |

| E0C6004      | S1C60N04 |

| E0C6005      | S1C60N05 |

| E0C6006      | S1C60N06 |

| E0C6007      | S1C60N07 |

| E0C6008      | S1C60N08 |

| E0C6009      | S1C60N09 |

| E0C6011      | S1C60N11 |

| E0C6013      | S1C60N13 |

| E0C6014      | S1C60140 |

| E0C60R08     | S1C60R08 |

#### S1C62 Family processors

| Previous No. | New No.  | Previous No. | New No.  |

|--------------|----------|--------------|----------|

| E0C621A      | S1C621A0 | E0C6247      | S1C62470 |

| E0C6215      | S1C62150 | E0C6248      | S1C62480 |

| E0C621C      | S1C621C0 | E0C6S48      | S1C6S480 |

| E0C6S27      | S1C6S2N7 | E0C624C      | S1C624C0 |

| E0C6S37      | S1C6S3N7 | E0C6251      | S1C62N51 |

| E0C623A      | S1C6N3A0 | E0C6256      | S1C62560 |

| E0C623E      | S1C6N3E0 | E0C6292      | S1C62920 |

| E0C6S32      | S1C6S3N2 | E0C6262      | S1C62N62 |

| E0C6233      | S1C62N33 | E0C6266      | S1C62660 |

| E0C6235      | S1C62N35 | E0C6274      | S1C62740 |

| E0C623B      | S1C6N3B0 | E0C6281      | S1C62N81 |

| E0C6244      | S1C62440 | E0C6282      | S1C62N82 |

| E0C624A      | S1C624A0 | E0C62M2      | S1C62M20 |

| E0C6S46      | S1C6S460 | E0C62T3      | S1C62T30 |

## Comparison table between new and previous number of development tools

Development tools for the S1C60/62 Family

| Previous No. | New No.     | Previous No. | New No.      |

|--------------|-------------|--------------|--------------|

| ASM62        | S5U1C62000A | DEV6262      | S5U1C62620D  |

| DEV6001      | S5U1C60N01D | DEV6266      | S5U1C62660D  |

| DEV6002      | S5U1C60N02D | DEV6274      | S5U1C62740D  |

| DEV6003      | S5U1C60N03D | DEV6292      | S5U1C62920D  |

| DEV6004      | S5U1C60N04D | DEV62M2      | S5U1C62M20D  |

| DEV6005      | S5U1C60N05D | DEV6233      | S5U1C62N33D  |

| DEV6006      | S5U1C60N06D | DEV6235      | S5U1C62N35D  |

| DEV6007      | S5U1C60N07D | DEV6251      | S5U1C62N51D  |

| DEV6008      | S5U1C60N08D | DEV6256      | S5U1C62560D  |

| DEV6009      | S5U1C60N09D | DEV6281      | S5U1C62N81D  |

| DEV6011      | S5U1C60N11D | DEV6282      | S5U1C62N82D  |

| DEV60R08     | S5U1C60R08D | DEV6S27      | S5U1C6S2N7D  |

| DEV621A      | S5U1C621A0D | DEV6S32      | S5U1C6S3N2D  |

| DEV621C      | S5U1C621C0D | DEV6S37      | S5U1C6S3N7D  |

| DEV623B      | S5U1C623B0D | EVA6008      | S5U1C60N08E  |

| DEV6244      | S5U1C62440D | EVA6011      | S5U1C60N11E  |

| DEV624A      | S5U1C624A0D | EVA621AR     | S5U1C621A0E2 |

| DEV624C      | S5U1C624C0D | EVA621C      | S5U1C621C0E  |

| DEV6248      | S5U1C62480D | EVA6237      | S5U1C62N37E  |

| DEV6247      | S5U1C62470D | EVA623A      | S5U1C623A0E  |

| Previous No.         New No.           EVA623B         S5U1C623B0E           EVA623F         S5U1C623B0E           EVA6247         S5U1C62470E           EVA6248         S5U1C62480E           EVA6256R         S5U1C62N51E1           EVA6256S         S5U1C62N56E           EVA6262S         S5U1C6260E           EVA6274S         S5U1C62740E           EVA6281S         S5U1C62N81E           EVA6282S         S5U1C62N82E           EVA6281S         S5U1C62N82E           EVA6281S         S5U1C62N82E           EVA6281S         S5U1C62N82E           EVA627S         S5U1C62N30E           EVA6S27S         S5U1C63N2E2           EVA6S32RS         S5U1C63N2E2           ICE62RS         S5U1C62000H           KIT6003S         S5U1C60N03K           KIT6004S         S5U1C60N07K |              |              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|

| EVA623E S5U1C623E0E EVA6247 S5U1C62470E EVA6248 S5U1C62480E EVA6251R S5U1C62N51E1 EVA6256 S5U1C62050E EVA6262 S5U1C62600E EVA6274 S5U1C62740E EVA6281 S5U1C62740E EVA6282 S5U1C62N81E EVA6281 S5U1C62N81E EVA6281 S5U1C62N82E EVA62M1 S5U1C62N10E EVA6273 S5U1C62N30E EVA6273 S5U1C63N7E EVA6827 S5U1C6S3N7E EVA6832R S5U1C6S3N2E2 ICE62R S5U1C60N03K KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                    | Previous No. | New No.      |

| EVA6247 S5U1C62470E EVA6248 S5U1C62480E EVA6251R S5U1C62N51E1 EVA6256 S5U1C62N56E EVA6262 S5U1C62600E EVA6264 S5U1C62600E EVA6264 S5U1C62740E EVA6281 S5U1C62N81E EVA6282 S5U1C62N81E EVA6281 S5U1C62N81E EVA6281 S5U1C62N81E EVA6282 S5U1C62N81E EVA6283 S5U1C62N81E EVA62T3 S5U1C62N10E EVA62T3 S5U1C6SN7E EVA6S32R S5U1C6SN2E2 ICE62R S5U1C60N03K KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                     | EVA623B      | S5U1C623B0E  |

| EVA6248 S5U1C62480E EVA6251R S5U1C62N51E1 EVA6256 S5U1C62N56E EVA6262 S5U1C62600E EVA6266 S5U1C62600E EVA6274 S5U1C62740E EVA6281 S5U1C62N81E EVA6282 S5U1C62N81E EVA6281 S5U1C62N81E EVA6287 S5U1C62N80E EVA6273 S5U1C62N10E EVA6273 S5U1C6SN7E EVA6S32R S5U1C6SN7E EVA6S32R S5U1C6SN0E2 KIT6003 S5U1C60N03K KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EVA623E      | S5U1C623E0E  |

| EVA6251R S5U1C62N51E1 EVA6256 S5U1C62N56E EVA6262 S5U1C62620E EVA6266 S5U1C6260E EVA6274 S5U1C62740E EVA6281 S5U1C62N81E EVA6282 S5U1C62N81E EVA6281 S5U1C62N81E EVA6287 S5U1C62N82E EVA62M1 S5U1C62T30E EVA62T3 S5U1C6S2N72 EVA6S32R S5U1C6SN2E2 ICE62R S5U1C60N03K KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EVA6247      | S5U1C62470E  |

| EVA6256 S5U1C62N56E<br>EVA6262 S5U1C62620E<br>EVA6266 S5U1C62660E<br>EVA6274 S5U1C62740E<br>EVA6281 S5U1C62N81E<br>EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EVA6248      | S5U1C62480E  |

| EVA6262 S5U1C62620E<br>EVA6266 S5U1C62660E<br>EVA6274 S5U1C62740E<br>EVA6281 S5U1C62N81E<br>EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EVA6251R     | S5U1C62N51E1 |

| EVA6266 S5U1C62660E<br>EVA6274 S5U1C62740E<br>EVA6281 S5U1C62N81E<br>EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EVA6256      | S5U1C62N56E  |

| EVA6274 S5U1C62740E<br>EVA6281 S5U1C62N81E<br>EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C6C900H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EVA6262      | S5U1C62620E  |

| EVA6281 S5U1C62N81E<br>EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S227 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C6C000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EVA6266      | S5U1C62660E  |

| EVA6282 S5U1C62N82E<br>EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S227 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C6C2000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EVA6274      | S5U1C62740E  |

| EVA62M1 S5U1C62M10E<br>EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EVA6281      | S5U1C62N81E  |

| EVA62T3 S5U1C62T30E<br>EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EVA6282      | S5U1C62N82E  |

| EVA6S27 S5U1C6S2N7E<br>EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EVA62M1      | S5U1C62M10E  |

| EVA6S32R S5U1C6S3N2E2<br>ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EVA62T3      | S5U1C62T30E  |

| ICE62R S5U1C62000H<br>KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | EVA6S27      | S5U1C6S2N7E  |

| KIT6003 S5U1C60N03K<br>KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EVA6S32R     | S5U1C6S3N2E2 |

| KIT6004 S5U1C60N04K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ICE62R       | S5U1C62000H  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | KIT6003      | S5U1C60N03K  |

| KIT6007 S5U1C60N07K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | KIT6004      | S5U1C60N04K  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | KIT6007      | S5U1C60N07K  |

<sup>\*2:</sup> Actual versions are not written in the manuals.

# S1C621A0 • Technical Hardware

#### **CONTENTS**

| CHAPTER 1 | DESCRIPTION I-1 |                                                                                                                     |                      |  |  |

|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

|           | 1.1             | Features                                                                                                            | I-1                  |  |  |

|           | 1.2             | Block Diagram                                                                                                       | I-3                  |  |  |

|           | 1.3             | Pin Configuration                                                                                                   | I-4                  |  |  |

|           | 1.4             | Pin Description                                                                                                     | I-5                  |  |  |

| CHAPTER 2 | CPU             | , ROM AND RAM                                                                                                       | I-6                  |  |  |

|           | 2.1             | CPU                                                                                                                 | I-6                  |  |  |

|           | 2.2             | ROM                                                                                                                 | I-6                  |  |  |

|           | 2.3             | RAM                                                                                                                 | I-7                  |  |  |

| CHAPTER 3 | PERI            | PHERAL CIRCUITS                                                                                                     | I-8                  |  |  |

|           | 3.1             | Memory Map                                                                                                          | I-8                  |  |  |

|           | 3.2             | Power Supply  Oscillation circuit power supply (VS1)  LCD power supply                                              | I-13                 |  |  |

|           | 3.3             | Oscillation Circuit                                                                                                 | I-16                 |  |  |

|           | 3.4             | Input Ports (K00–K03, K10–K13)                                                                                      | I-18<br>I-19         |  |  |

|           | 3.5             | Output Ports (R00–R03, R10–R13, R20)                                                                                | I-20<br>I-21         |  |  |

|           | 3.6             | I/O Ports (P00–P03)  Output data  Input data  I/O control (IOC) register  Notes on operation with pull-up resistors | I-25<br>I-26<br>I-26 |  |  |

| •           | 3.7   | Segment assignment                                                                                               |                                              |

|-------------|-------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|             |       | Timer                                                                                                            | I-31<br>I-31<br>I-32<br>I-33<br>I-34         |

|             |       | REM control registers  Soft-timer mode  Hard-timer mode  Initializing REM circuit  REM circuit programming notes | I-38<br>I-40<br>I-46                         |

| 3           | 3.10  | AMP and SVD  AMP (MOS input analog comparator)                                                                   | I-49                                         |

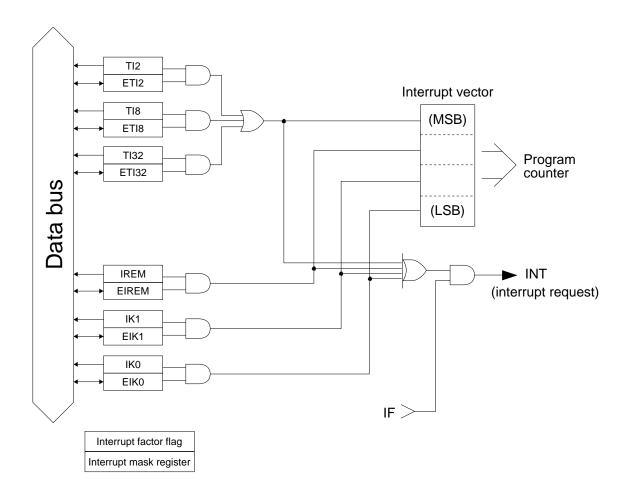

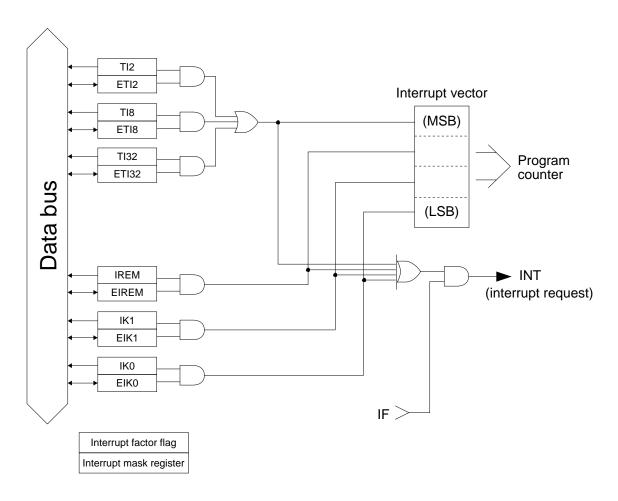

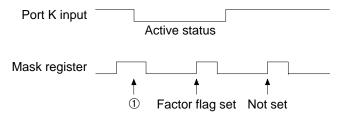

| 3           | 3.11  | Interrupt and Halt  Interrupt request  Interrupt mask register  Interrupt vector                                 | I-53<br>I-57                                 |

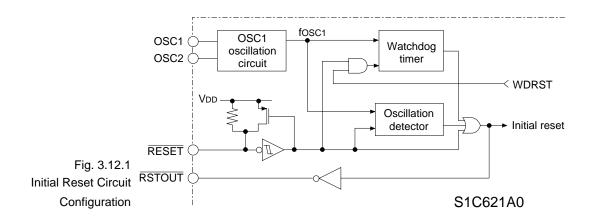

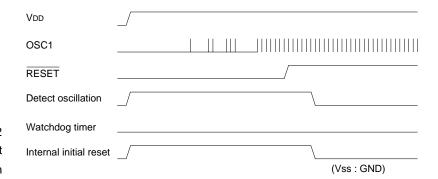

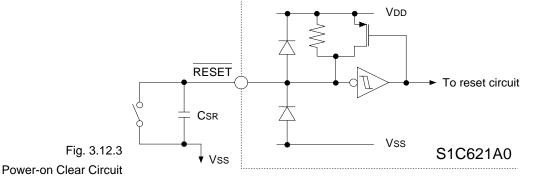

|             |       | Initial Reset                                                                                                    | I-60<br>I-61<br>I-62<br>I-62<br>I-63<br>I-63 |

|             |       | Test Input Pin (TEST)  Lower Current Dissipation                                                                 |                                              |

| CHAPTER 4 1 | TYPIC | CAL EXTERNAL CONNECTION                                                                                          | I-66                                         |

| CHAPTER 5 | ELEC | CTRICAL CHARACTERISTICS                                                   | I-67         |

|-----------|------|---------------------------------------------------------------------------|--------------|

|           | 5.1  | Absolute Maximum Ratings                                                  | I-67         |

|           | 5.2  | Recommended Operating Conditions                                          | I-67         |

|           | 5.3  | DC Characteristics                                                        | I-68         |

|           | 5.4  | Analog Circuit Characteristics and Current Dissipation                    | I-69         |

|           | 5.5  | Oscillation Characteristics                                               | I-70         |

|           | 5.6  | Input Current Characteristics (For Reference)                             | I-72         |

|           | 5.7  | Output Current Characteristics (For Reference)                            | I-74         |

| CHAPTER 6 | PAC  | CKAGE                                                                     | I-76         |

|           | 6.1  | Plastic Package                                                           | I-76         |

|           | 6.2  | Ceramic Package for Test Sample                                           | I-77         |

| CHAPTER 7 | PAC  | LAYOUT                                                                    | I-78         |

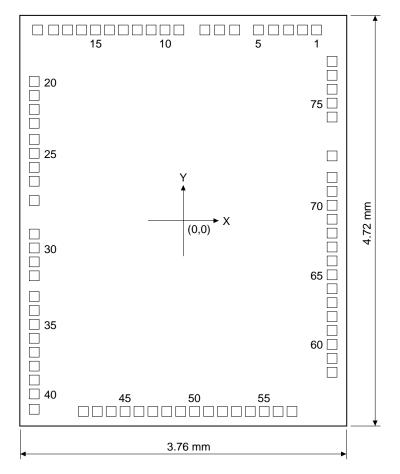

|           | 7.1  | Pad Layout Diagram                                                        | I-78         |

|           | 7.2  | Pad Coordinates                                                           | I-79         |

| CHAPTER 8 |      | ERENCES BETWEEN S1C621A0 AND S1C6214 evious number, discontinued product) | I-80         |

|           | 8.1  | Description                                                               | I-80         |

|           | 8.2  | Differences                                                               | I-80<br>I-82 |

### CHAPTER 1 DESCRIPTION

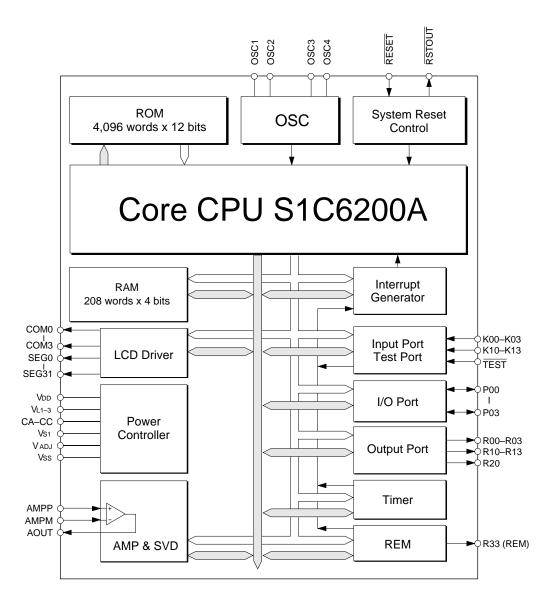

The S1C621A0 is a single-chip microcomputer which uses an S1C6200A CMOS 4-bit CPU as the core. It contains a 4,096 (words)  $\times$  12 (bits) ROM, 208 (words)  $\times$  4 (bits) RAM, LCD driver circuit, remote-control carrier output circuit, time base counter, analog comparator, and watchdog timer.

The S1C621A0 offers a superb solution to infrared remote controller and other applications requiring low power consumption.

#### 1.1 Features

• ROM size:  $4.096 \text{ words} \times 12 \text{ bits}$

RAM size: 208 words × 4 bits

• Clock: 32.768 kHz or 455 kHz (selected by software)

Instruction execution

time:

32 kHz operation 153, 214 or 366 μsec (depending on instructions) 455 kHz operation 11, 15 or 26 μsec (depending on instructions)

Instruction set: 100 instructions

• Input ports: 8 ports (with or without pull-up resistor)

Output ports: 9 ports (clock output and buzzer output possible by

using mask option)

I/O ports: 4 ports

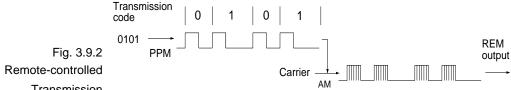

Infrared remote-control 1 output

output:

• LCD drivers: 32 segment × 3 common outputs

32 segment  $\times$  4 common outputs

(Duty 1/3 or 1/4 selected by using mask option)

Crystal oscillation circuit: 32.768 kHz

• Ceramic oscillation 455 kHz (Alternative selections of either not using this

circuit or using CR oscillation circuit instead is

possible by using mask option)

Interrupts:

circuit:

External 2 input interrupts

Internal 3 timer interrupts (32 Hz, 8 Hz or 2 Hz)

1 remote control output control interrupt

SVD built-in: Detection voltage 2.3 V

• Power supply: 3 V (2.2 V to 3.5 V)

· Current consumption

(Typ.):

32 kHz operation 2 µA in halt mode

$9 \mu A$  in full run mode

455 kHz operation 130 μA

• Supply form: QFP5-80pin, QFP14-80pin or chip

# 1.2 Block Diagram

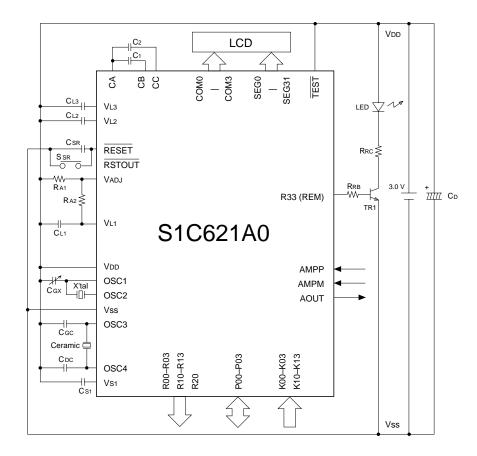

Fig. 1.2.1 S1C621A0 Block Diagram

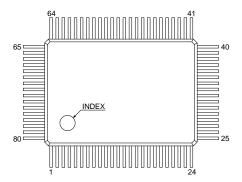

# 1.3 Pin Configuration

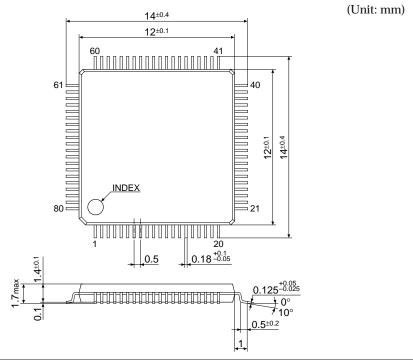

# QFP5-80pin (plastic)

Fig. 1.3.1 S1C621A0 Pin Configuration (QFP5-80pin)

| Pin No. | Pin Name | Pin No. | Pin Name        | Pin No. | Pin Name | Pin No. | Pin Name |

|---------|----------|---------|-----------------|---------|----------|---------|----------|

| 1       | SEG16    | 21      | COM0            | 41      | OSC4     | 61      | K11      |

| 2       | SEG15    | 22      | CC              | 42      | Vs1      | 62      | K12      |

| 3       | SEG14    | 23      | CB              | 43      | R00      | 63      | K13      |

| 4       | SEG13    | 24      | CA              | 44      | R01      | 64      | TEST     |

| 5       | SEG12    | 25      | VL3             | 45      | R02      | 65      | N.C.     |

| 6       | SEG11    | 26      | VL2             | 46      | R03      | 66      | SEG31    |

| 7       | SEG10    | 27      | RESET           | 47      | R10      | 67      | SEG30    |

| 8       | SEG9     | 28      | VADJ            | 48      | R11      | 68      | SEG29    |

| 9       | SEG8     | 29      | V <sub>L1</sub> | 49      | R12      | 69      | SEG28    |

| 10      | SEG7     | 30      | R33(REM)        | 50      | R13      | 70      | SEG27    |

| 11      | SEG6     | 31      | RSTOUT          | 51      | R20      | 71      | SEG26    |

| 12      | SEG5     | 32      | AMPP            | 52      | P00      | 72      | SEG25    |

| 13      | SEG4     | 33      | AMPM            | 53      | P01      | 73      | SEG24    |

| 14      | SEG3     | 34      | AOUT            | 54      | P02      | 74      | SEG23    |

| 15      | SEG2     | 35      | VDD             | 55      | P03      | 75      | SEG22    |

| 16      | SEG1     | 36      | N.C.            | 56      | K00      | 76      | SEG21    |

| 17      | SEG0     | 37      | OSC1            | 57      | K01      | 77      | SEG20    |

| 18      | COM3     | 38      | OSC2            | 58      | K02      | 78      | SEG19    |

| 19      | COM2     | 39      | Vss             | 59      | K03      | 79      | SEG18    |

| 20      | COM1     | 40      | OSC3            | 60      | K10      | 80      | SEG17    |

N.C. = No Connection

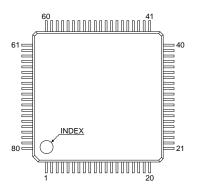

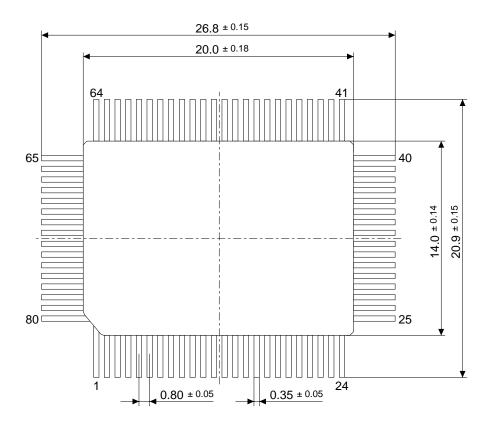

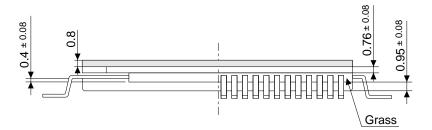

# QFP14-80pin (plastic)

Fig. 1.3.2 S1C621A0 Pin Configuration (QFP14-80pin)

| Pin No. | Pin Name |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | CB       | 21      | R01      | 41      | TEST     | 61      | SEG14    |

| 2       | CA       | 22      | R02      | 42      | N.C.     | 62      | SEG13    |

| 3       | VL3      | 23      | R03      | 43      | SEG31    | 63      | SEG12    |

| 4       | VL2      | 24      | R10      | 44      | SEG30    | 64      | SEG11    |

| 5       | RESET    | 25      | R11      | 45      | SEG29    | 65      | SEG10    |

| 6       | Vadj     | 26      | R12      | 46      | SEG28    | 66      | SEG9     |

| 7       | VL1      | 27      | R13      | 47      | SEG27    | 67      | SEG8     |

| 8       | R33(REM) | 28      | R20      | 48      | SEG26    | 68      | SEG7     |

| 9       | RSTOUT   | 29      | P00      | 49      | SEG25    | 69      | SEG6     |

| 10      | AMPP     | 30      | P01      | 50      | SEG24    | 70      | SEG5     |

| 11      | AMPM     | 31      | P02      | 51      | SEG23    | 71      | SEG4     |

| 12      | AOUT     | 32      | P03      | 52      | SEG22    | 72      | SEG3     |

| 13      | Vdd      | 33      | K00      | 53      | SEG21    | 73      | SEG2     |

| 14      | OSC1     | 34      | K01      | 54      | SEG20    | 74      | SEG1     |

| 15      | OSC2     | 35      | K02      | 55      | SEG19    | 75      | SEG0     |

| 16      | Vss      | 36      | K03      | 56      | SEG18    | 76      | COM3     |

| 17      | OSC3     | 37      | K10      | 57      | SEG17    | 77      | COM2     |

| 18      | OSC4     | 38      | K11      | 58      | SEG16    | 78      | COM1     |

| 19      | Vs1      | 39      | K12      | 59      | N.C.     | 79      | COM0     |

| 20      | R00      | 40      | K13      | 60      | SEG15    | 80      | CC       |

N.C. = No Connection

# 1.4 Pin Description

Table 1.4.1 Pin Description

| 5: 1:           | Pin     | No.      |          |                                             |

|-----------------|---------|----------|----------|---------------------------------------------|

| Pin Name        | QFP5-80 | QFP14-80 | In / Out | Function                                    |

| V <sub>DD</sub> | 35      | 13       | I        | Power supply (+)                            |

| Vss             | 39      | 16       | I        | Power supply (-)                            |

| Vsı             | 42      | 19       | _        | Oscillation circuit power supply            |

|                 |         |          |          | (about VDD -2.0 V)                          |

| Vl1             | 29      | 7        | _        | LCD power supply (VDD -VL)                  |

| V <sub>L2</sub> | 26      | 4        | _        | LCD booster supply (VDD -2VL)               |

| VL3             | 25      | 3        | _        | LCD booster supply (VDD -3VL)               |

| CA-CC           | 22–24   | 1, 2, 80 | _        | LCD booster capacitor connection pin        |

| Vadj            | 28      | 6        | I        | VL input adjustment pin                     |

| OSC1            | 37      | 14       | I        | Crystal oscillation input pin               |

| OSC2            | 38      | 15       | О        | Crystal oscillation output pin              |

|                 |         |          |          | (include drain capacitor)                   |

| OSC3            | 40      | 17       | I        | Ceramic or CR oscillation input pin         |

|                 |         |          |          | (selected by using mask option)             |

| OSC4            | 41      | 18       | О        | Ceramic or CR oscillation output pin        |

|                 |         |          |          | (selected by using mask option)             |

| COM0-3          | 18–21   | 76–79    | О        | LCD common outputs (duty 1/3 or 1/4         |

|                 |         |          |          | selected possible by using mask option)     |

| SEG0-31         | 1–17    | 43–58    | О        | LCD segment outputs (DC output              |

|                 | 66–80   | 60–75    |          | possible by using mask option)              |

| AMPP            | 32      | 10       | I        | Analog comparator non-inverted input pin    |

| AMPM            | 33      | 11       | I        | Analog comparator inverted input pin        |

| AOUT            | 34      | 12       | О        | Analog comparator output pin                |

| TEST            | 64      | 41       | I        | Test input pin                              |

| RESET           | 27      | 5        | I        | Initial reset input pin                     |

| K00-03          | 56–59   | 33–36    | I        | Input pins                                  |

| K10-13          | 60–63   | 37–39    | I        | Input pins                                  |

| P00-03          | 52–55   | 29–32    | I/O      | I/O pins                                    |

| R00-03          | 43–46   | 20–23    | О        | Output pins                                 |

|                 |         |          |          | (R12 : DC, FOUT or $\overline{BZ}$ selected |

| R10–13          | 47–50   | 24–27    |          | by using mask option)                       |

|                 |         |          |          | (R13 : DC or BZ selected by using           |

| R20             | 51      | 28       |          | mask option)                                |

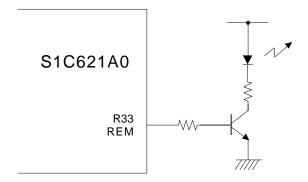

| R33 (REM)       | 30      | 8        | О        | Remote control carrier output pin           |

| RSTOUT          | 31      | 9        | О        | Initial reset output pin                    |

# CHAPTER 2 CPU, ROM AND RAM

#### 2.1 CPU

The S1C621A0 uses an S1C6200A 4-bit CPU as the core and therefore has nearly the same register composition and instruction set as other family processors using the S1C6200A core CPU. (For details of the S1C6200A, see the "S1C6200/6200A Core CPU Manual".)

Due to features such as the ROM/RAM size and two clock operating modes, the S1C621A0 differs from the S1C6200A in the following points:

- (1) The index registers IX and IY each consist of 8 bits as the RAM can be addressed on a 8-bit basis. (The register has no 4-bit page part.) Therefore, the instructions relating to XP and YP ("PUSH XP", "PUSH YP", "LD XP,r", "LD YP,r", "LD r,XP" and "LD r,YP") cannot be used with the S1C621AO.

- (2) The S1C621A0 does not support the sleep mode. The SLP instruction is therefore unavailable with the S1C621A0.

- (3) Since the ROM had a size of 4,096 words, no bank bit is required. The S1C621A0 thus uses no PCB or NBP registers.

#### 2.2 **ROM**

The S1C621A0 has a mask ROM for storage of programs. Its size is 4,096 words  $\times$  12 bits.

The program area consists of 16 pages, each having 256 steps. After initial reset, the program starting address is page 1, step 0. The interrupt vector addresses range from steps 01H to 0FH of page 1.

#### 2.3 **RAM**

This RAM stores various data. It is also used as a stack area from which subroutines are called or into which registers are saved. As the size of the RAM is  $208 \text{ words} \times 4 \text{ bits}$ , the stack area must be set at addresses up to CFH. (For the RAM map, see section 3.1 "Memory Map".)

In programming the RAM, it is necessary that the data area be separated from the stack area. (A stack area of 3 words is needed for subroutine call, interrupt handling, etc.)

The RAM area at addresses from 00H to 0FH accommodates memory registers which are addressed by the register pointer RP.

## CHAPTER 3 PERIPHERAL CIRCUITS

All peripheral circuits (timer, I/O, etc.) of the S1C621A0 are configured in memory-mapped I/O form, and can be controlled by using memory operation instructions. This section describes the operation of each peripheral circuit in detail.

## 3.1 Memory Map

The data memory (RAM) of the S1C621A0 has an address space of 256 words, of which the high-order 48 words are allocated to the peripheral circuits.

Figure 3.1.1 shows the S1C621A0 memory map. Tables 3.1.1(a) to 3.1.1(d) gives details of the I/O memory map (addresses from 0F0H to 0FFH).

| Address | Low  |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---------|------|------------------------------------|-------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|         |      | 0                                  | 1                                         | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В  | С  | D  | E  | F  |

| Page    | High |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 0    | MO                                 | M1                                        | M2 | МЗ | M4 | M5 | M6 | M7 | M8 | М9 | MA | MB | МС | MD | ME | MF |

|         | 1    |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 2    |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 3    |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 4    |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 5    |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 6    |                                    | RAM (208 words x 4 bits)                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 7    |                                    | R/W                                       |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 0       | 8    |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | 9    |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | Α    |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | В    |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | С    |                                    |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | D    | Display memory (32 words x 4 bits) |                                           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|         | Е    |                                    |                                           |    |    |    |    |    | V  |    |    |    | ,  |    |    |    |    |

|         | F    |                                    | I/O memory [See Tables 3.1.1(a)-3.1.1(d)] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

Fig. 3.1.1 Memory Map

Note Memory is not mounted in unused area within the memory map and in memory area not indicated in this chapter. For this reason, normal operation cannot be assured for programs that have been prepared with access to these areas.

Table 3.1.1(a) I/O memory map (0F0H-0F3H)

| Address |       | Regi  | ster |       |        |       |                                      |                    | Comment                                                      |

|---------|-------|-------|------|-------|--------|-------|--------------------------------------|--------------------|--------------------------------------------------------------|

| Address | D3    | D2    | D1   | D0    | Name   | Init  | 1                                    | 0                  | Comment                                                      |

|         | REMSO | IREM  | IK1  | IK0   | REMSO  | 0     | On                                   | Off                | Forced REM output (on/off)                                   |

|         | R/W   |       | R    |       | IREM   | х     | Yes                                  | No                 | Interrupt factor flag (REM) Clear to 0 after read            |

| 0F0H    |       |       |      |       | IK1    | 0     | Yes                                  | No                 | Interrupt factor flag (K10–K13)  Clear to 0 after read       |

|         |       |       |      |       | IK0    | 0     | Yes                                  | No                 | Interrupt factor flag (K00–K03) Clear to 0 after read        |

|         | WDRST | TI2   | TI8  | TI32  | WDRST  | Clear | Clear                                | -                  | Watchdog timer reset                                         |

| .=      | W R   |       |      |       | TI2    | 0     | Yes                                  | No                 | Interrupt factor flag (Timer 2 Hz) Clear to 0 after read     |

| 0F1H    |       |       |      |       | TI8    | 0     | Yes                                  | No                 | Interrupt factor flag (Timer 8 Hz)  Clear to 0 after read    |

|         |       |       |      |       | Tl32   | 0     | Yes                                  | No                 | Interrupt factor flag (Timer 32 Hz)<br>Clear to 0 after read |

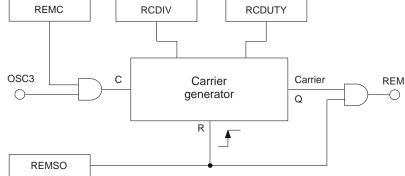

|         | REMC  | EIREM | EIK1 | EIK0  | REMC   | 1     | On                                   | Off                | REM carrier generation on/off                                |

| 0F2H    |       | R/    | W    |       | EIREM  | 0     | Enable                               | Mask               | Interrupt mask register (REM)                                |

| 01 211  |       |       |      |       | EIK1   | 0     | Enable                               | Mask               | Interrupt mask register (K10–K13)                            |

|         |       |       |      |       | EIK0   | 0     | Enable                               | Mask               | Interrupt mask register (K00–K03)                            |

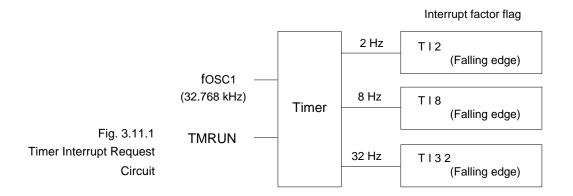

|         | TMRUN | ETI2  | ETI8 | ETI32 | TMRUN  | 0     | Run                                  | Clear<br>&<br>Stop | Timer Run/Clear & Stop                                       |

| 0F3H    | R/W   |       | ETI2 | 0     | Enable | Mask  | Interrupt mask register (Timer 2 Hz) |                    |                                                              |

| UF3H    |       |       |      |       | ETI8   | 0     | Enable                               | Mask               | Interrupt mask register (Timer 8 Hz)                         |

|         |       |       |      |       | ETI32  | 0     | Enable                               | Mask               | Interrupt mask register (Timer 32 Hz)                        |

Table 3.1.1(b) I/O memory map (0F4H-0F7H)

| Address |       | Reg    | ister  |      |        |      |                      |                              | Comment                       |

|---------|-------|--------|--------|------|--------|------|----------------------|------------------------------|-------------------------------|

| Address | D3    | D2     | D1     | D0   | Name   | Init | 1                    | 0                            | Comment                       |

|         | TM03  | TM02   | TM01   | TM00 | TM03   | 0    |                      |                              | Timer data (low-order) 16 Hz  |

| 0F4H    |       | I      | R      |      | TM02   | 0    |                      |                              | Timer data (low-order) 32 Hz  |

| UF4H    |       |        |        |      | TM01   | 0    |                      |                              | Timer data (low-order) 64 Hz  |

|         |       |        |        |      | TM00   | 0    |                      |                              | Timer data (low-order) 128 Hz |

|         | TM13  | TM12   | TM11   | TM10 | TM13   | 0    |                      |                              | Timer data (High-order) 1 Hz  |

| 0F5H    | R     |        |        | TM12 | 0      |      |                      | Timer data (High-order) 2 Hz |                               |

| 01-311  |       |        |        |      | TM11   | 0    |                      |                              | Timer data (High-order) 4 Hz  |

|         |       |        |        |      | TM10   | 0    |                      |                              | Timer data (High-order) 8 Hz  |

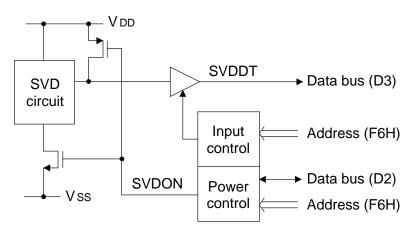

|         | SVDDT | SVDON  | CLKCHG | OSCC | SVDDT  | -    | Normal               | Low<br>voltage               | SVD data (1 when SVDON = 0)   |

| 0F6H    | R     |        | R/W    |      | SVDON  | 0    | On                   | Off                          | SVD circuit on/off            |

| UFOR    |       |        |        |      | CLKCHG | 0    | OSC1                 | OSC3                         | CPU CLK change OSC1/OSC3      |

|         |       |        |        |      | oscc   | 1    | On                   | Off                          | OSC3 oscillation on/off       |

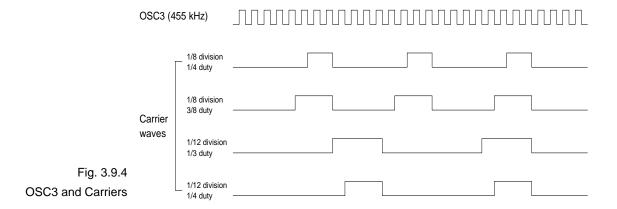

|         | RCDIV | RCDUTY | RT1    | RT0  | RCDIV  | х    |                      |                              | REM carrier cycle set         |

| 0F7H    | R/W   |        | RCDUTY | х    |        |      | REM carrier duty set |                              |                               |

| 01-711  |       |        |        |      | RT1    | х    |                      |                              | REM τ-cycle set               |

|         |       |        |        | RT0  | х      |      |                      | REM τ-cycle set              |                               |

Table 3.1.1(c) I/O memory map (0F8H-0F9H, 0FAH-0FBH)

| Address |       | Reg   | ister |      |       |      |                                      |                                      | Comment                                                             |

|---------|-------|-------|-------|------|-------|------|--------------------------------------|--------------------------------------|---------------------------------------------------------------------|

| Address | D3    | D2    | D1    | D0   | Name  | Init | 1                                    | 0                                    | Comment                                                             |

|         | RIC3  | RIC2  | RIC1  | RIC0 | RIC3  | х    |                                      |                                      | REM interrupt counter set ( τ clock) (all :1 after count completed) |

| 0F8H    |       | V     | V     |      | RIC2  | x    |                                      |                                      | (an . r arter count completed)                                      |

| 01 011  |       |       |       |      | RIC1  | х    |                                      |                                      |                                                                     |

|         |       |       | ,     |      | RIC0  | х    |                                      |                                      |                                                                     |

|         | ROUT1 | ROUT0 | MF91  | MF90 | ROUT1 | 0    |                                      |                                      | REM output-on time set (0 $\tau$ – 3 $\tau$ )                       |

| 0F9H    | R/W   |       |       |      | ROUT0 | 0    |                                      |                                      | REM output-on time set (0 $\tau$ – 3 $\tau$ )                       |

| 01 011  |       |       |       |      | MF91  | х    |                                      |                                      | General-purpose register (bit)                                      |

|         |       | ,     |       |      | MF90  | х    |                                      |                                      | General-purpose register (bit)                                      |

|         | K03   | K02   | K01   | K00  | K03   | _    | High                                 | Low                                  | Input port (fall : interrupt factor)                                |

| 0FAH    |       | F     | ₹     |      | K02   | _    | High                                 | Low                                  | Input port (fall : interrupt factor)                                |

| UFAIT   |       |       |       |      | K01   | -    | High                                 | Low                                  | Input port (fall : interrupt factor)                                |

|         |       |       |       |      | K00   | -    | High                                 | Low                                  | Input port (fall : interrupt factor)                                |

|         | K13   | K12   | K11   | K10  | K13   | -    | High                                 | Low                                  | Input port (fall : interrupt factor)                                |

| 0FBH    | R     |       | K12   | _    | High  | Low  | Input port (fall : interrupt factor) |                                      |                                                                     |

|         |       |       |       |      | K11   | _    | High                                 | Low                                  | Input port (fall : interrupt factor)                                |

|         |       |       |       | K10  | -     | High | Low                                  | Input port (fall : interrupt factor) |                                                                     |

Table 3.1.1(d) I/O memory map (0FCH-0FFH)

| Address |       | Reg  | ister |     |      |      |                          |     | Comment                                           |

|---------|-------|------|-------|-----|------|------|--------------------------|-----|---------------------------------------------------|

| Address | D3    | D2   | D1    | D0  | Name | Init | 1                        | 0   | Comment                                           |

|         | R03   | R02  | R01   | R00 | R03  | 1    | High                     | Low | Output port                                       |

| 0FCH    |       | R    | /W    |     | R02  | 1    | High                     | Low | Output port                                       |

| UPCH    |       |      |       |     | R01  | 1    | High                     | Low | Output port                                       |

|         |       |      |       |     | R00  | 1    | High                     | Low | Output port                                       |

|         | R13   | R12  | R11   | R10 | R13  | 1    | High                     | Low | Output port                                       |

| 0FDH    | R/W   |      |       |     | R12  | 1    | High                     | Low | Output port                                       |

| OFDIT   |       |      |       |     | R11  | 1    | High                     | Low | Output port                                       |

|         |       |      |       |     | R10  | 1    | High                     | Low | Output port                                       |

|         | P03   | P02  | P01   | P00 | P03  | 1    | High                     | Low | I/O port (used as input port after initial reset) |

| 0FEH    |       | R    | /W    |     | P02  | 1    | High                     | Low | I/O port (used as input port after initial reset) |

| OFEIT   |       |      |       |     | P01  | 1    | High                     | Low | I/O port (used as input port after initial reset) |

|         |       |      |       |     | P00  | 1    | High                     | Low | I/O port (used as input port after initial reset) |

|         | OPDT  | OPON | IOC   | R20 | OPDT | -    | High                     | Low | Analog comparator data (0 or 1)                   |

| VEEN    | R R/W |      | OPON  | 0   | On   | Off  | Analog comparator on/off |     |                                                   |

| 0FFH    |       |      |       |     | IOC  | 0    | Out                      | ln  | I/O port control out/in                           |

|         |       |      |       |     | R20  | 0    | High                     | Low | Output port                                       |

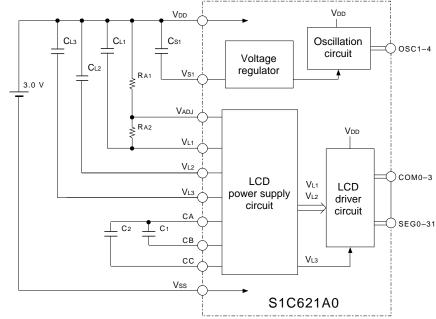

# 3.2 Power Supply

The S1C621A0 is given 3 V by an single external power supply and generates voltages needed to operate its LCD driver and oscillation circuit.

A voltage reduction can be detected by the on-chip supply voltage detection circuit. (See section 3.10 "AMP and SVD".)

Power Supply Block

Diagram

Fig. 3.2.1

Oscillation circuit power supply (Vs1)

The S1C621A0 uses its on-chip voltage regulator to generate voltage level VS1 for stabilization of the oscillation circuit.

#### LCD power supply

The on-chip voltage regulator and booster are used to generate voltage levels (VDD, VL1, VL2 and VL3) needed to drive the LCDs.

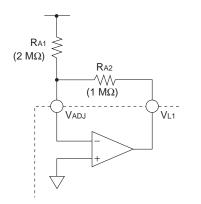

VL2 is obtained by boosting VL1 two times and VL3 is obtained by boosting VL1 three times. VL1 can be adjusted by feeding it back to the VADJ pin through RA1 and RA2 as shown in Figure 3.2.2. VL ( $\approx$  VDD - VL1) is defined by following equation:

$$VL \approx 1 x (RA1 + RA2) / RA1$$

Example:

| VL      | Ra1  | RA2  |

|---------|------|------|

| ≈ 1 V   | ∞    | Ω Ω  |

| ≈ 1.5 V | 2 MΩ | 1 MΩ |

An LCD driving voltage suited to each LCD panel can be obtained by adjusting VL at the VADJ pin.

VADJ

Fig. 3.2.2 VL Adjust Circuit

#### 3.3 Oscillation Circuit

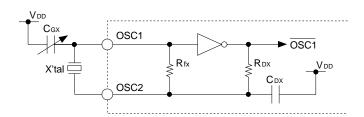

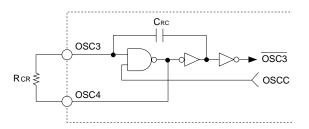

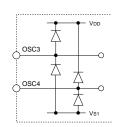

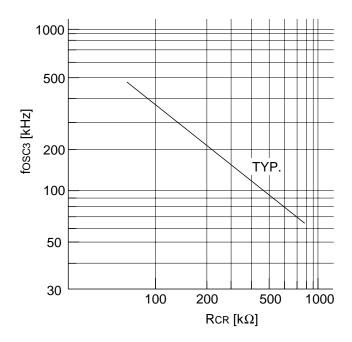

The S1C621A0 contains an OSC1 (32.768 kHz) crystal oscillation circuit and an OSC3 (455 kHz) ceramic oscillation circuit\*. Either the OSC1 or OSC3 can be selected as the CPU operation clock by software. Figures 3.3.1 and 3.3.2 show block diagrams of the oscillation circuit.

\* By using the mask option it is possible to connect a CR oscillation circuit in place of the ceramic oscillation circuit, or it is possible to forgo the use of the OSC3 circuit.

Fig. 3.3.1

OSC1 Oscillation Circuit

(Crystal)

a) OSC3 - CR oscillation circuit

VDD CGC OSC3 OSC3 OSC3 OSCC OSCC OSCC OSCC

Fig. 3.3.2 OSC3 Oscillation Circuit

b) OSC3 - Ceramic oscillation circuit

c) OSC3 – "Not Use" is selected by mask option

# Oscillation circuit control by software

As shown in Table 3.3.1, the oscillation circuit can be controlled by software using D1 and D0 at I/O memory address 0F6H.

Table 3.3.1 I/O Memory Map

| Address |       | Reg   | ister  |      |        |      |        |                | Comment                     |  |

|---------|-------|-------|--------|------|--------|------|--------|----------------|-----------------------------|--|

| Address | D3    | D2    | D1     | D0   | Name   | Init | 1      | 0              | Comment                     |  |

|         | SVDDT | SVDON | CLKCHG | OSCC | SVDDT  | -    | Normal | Low<br>voltage | SVD data (1 when SVDON = 0) |  |

| 0F6H    | R     |       | R/W    |      | SVDON  | 0    | On     | Off            | SVD circuit on/off          |  |

| UFOR    |       |       |        |      | CLKCHG | 0    | OSC1   | OSC3           | CPU CLK change OSC1/OSC3    |  |

|         |       |       |        |      | oscc   | 1    | On     | Off            | OSC3 oscillation on/off     |  |

Note: Init = value at initial reset, x = undefined, - = not set on the circuit

The following two bits relate to the oscillation circuit control by software.

OSCC: OSC3 oscillation circuit drive control

This bit controls OSC3 oscillation ON/OFF condition.

OSC3 oscillation is ON when OSCC = 1 and OFF when

OSCC = 0.

At initial reset, the OSC3 circuit is turned ON. The circuit must be turned ON when it is necessary to obtain a remote control carrier signal output or a faster CPU speed. In all other cases, the circuit must stay OFF to save power.

• CLKCHG: CPU clock frequency change

This bit selects either a CPU operation clock, OSC3 clock or OSC1 clock. The OSC3 clock is selected with CLKCHG = 0 and the OSC1 clock with CLKCHG = 1. At initial reset, the bit is 0 (OSC3 selected).

Table 3.3.2 lists the relation between the CPU clock frequency and instruction execution time.

Table 3.3.2 CPU Clock Frequency and Instruction Execution Time

| CDLL clock from upper | Instruction execution time |                     |                      |  |  |  |  |  |  |

|-----------------------|----------------------------|---------------------|----------------------|--|--|--|--|--|--|

| CPU clock frequency   | 5-clock instruction        | 7-clock instruction | 12-clock instruction |  |  |  |  |  |  |

| 32.768 kHz            | 152.6 μs                   | 213.6 μs            | 366.2 μs             |  |  |  |  |  |  |

| 455 kHz               | 11.0 µs                    | 15.4 μs             | 26.4 μs              |  |  |  |  |  |  |

#### **Programming notes**

- (1) The OSC3 clock must not be selected unless its oscillation is stable.

- (2) It takes at least 5 ms for the OSC3 clock (if generated by the 455 kHz ceramic oscillation circuit) to become stable after it is switched from OFF to ON. When changing the CPU clock from OSC3 to OSC1, wait at least 5 ms after OSC3 oscillation turns ON.

- (3) When changing the CPU clock from OSC3 to OSC1 (32 kHz) at power-on, wait at least 3 seconds after the initial reset is cleared.

- (4) The time until OSC3 or OSC1 oscillation becomes stable depends on the characteristics, operating conditions and other factors of the externally connected oscillator. Before using an oscillator, check its characteristics and set a proper waiting time with sufficient margin.

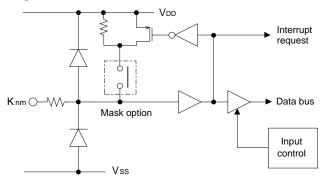

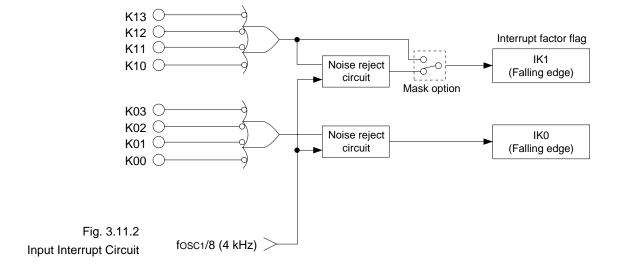

## 3.4 Input Ports (K00-K03, K10-K13)

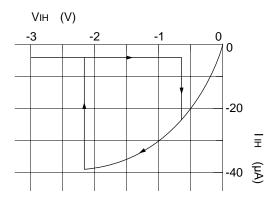

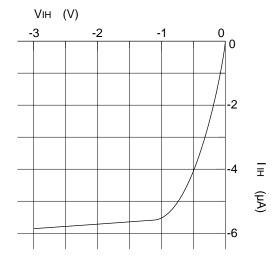

The S1C621A0 has two 4-bit general-purpose input ports (K00-K03 and K10-K13). As shown in Figure 3.4.1, each input port pin is provided with a pull-up and a feedback pull-up so that the port is suitable for push switch or key matrix switch input. As the pull-up can be removed by using mask option, the input port can also be used for slide switch input or interface with another LSI.

Fig. 3.4.1 Input Port Configuration

#### Input port data

Input port data can be read on a 4-bit basis (K00–K03, K10–K13) addressed 0FAH and 0FBH. Table 3.4.1 shows data assignments to the input port bits.

Table 3.4.1 I/O Memory Map

| Address |     | Reg | ister |     |      |      |      |     | Comment                              |

|---------|-----|-----|-------|-----|------|------|------|-----|--------------------------------------|

| Address | D3  | D2  | D1    | D0  | Name | Init | 1    | 0   | Confinent                            |

|         | K03 | K02 | K01   | K00 | K03  | -    | High | Low | Input port (fall : interrupt factor) |

| 0FAH    |     | !   | R     |     | K02  | _    | High | Low | Input port (fall : interrupt factor) |

| UFAH    |     |     |       |     | K01  | _    | High | Low | Input port (fall : interrupt factor) |

|         |     |     |       |     | K00  | -    | High | Low | Input port (fall : interrupt factor) |

|         | K13 | K12 | K11   | K10 | K13  | -    | High | Low | Input port (fall : interrupt factor) |

| 0FBH    |     | l   | R     |     | K12  | -    | High | Low | Input port (fall : interrupt factor) |

| OI BIT  |     |     |       |     | K11  | -    | High | Low | Input port (fall : interrupt factor) |

|         |     |     |       |     | K10  | -    | High | Low | Input port (fall : interrupt factor) |

Note: Init = value at initial reset, - = not set on the circuit

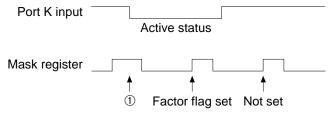

#### Input interrupt

An interrupt request to the CPU can be invoked by the falling edge of an input port pin. For details, see section 3.11 "Interrupts and Halt".

#### **Programming note**

If the Knm pin is used as an input with an on-chip pull-up resistor, the time constant of the input line capacitive load and on-chip pull-up resistor causes the logic level to change with a certain delay from the start of an input signal change.

For example, consider a key matrix combined with some N-channel open drain outputs where turning a switch ON causes the key scan program to start. Input data is read in such a way that all the N-channel open drain outputs, except one, are turned off to key-scan the input signal now at low level as a result of switch-on, and the switch between that output and the others is checked to determine has turned ON. Even with switch-off, however, reading data without a delay results in an input error (the input is at low level). To prevent this, data must be programmed to assure that it is read with a delay, or that all N-channel open drain outputs are turned OFF, followed by reading the input repeatedly to confirm that it returns to high level and turns one output ON, then read input data.

I-19

Please consider delay of inputs on the program.

# 3.5 Output Ports (R00-R03, R10-R13, R20)

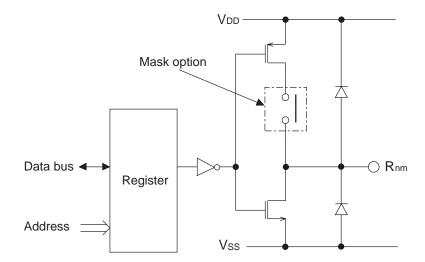

The S1C621A0 has two 4-bit and one 1-bit general-purpose output ports. As shown in Figure 3.5.1, the output may take either complementary or N-channel open drain form (selected by using mask option). Even with an open drain output, however, the Rnm pin cannot be pulled up to above VDD level.

Fig. 3.5.1

Output Port Configuration

#### Output port data

The output port is a read/write register as shown in Figure 3.5.1. The data in the register is output by the output port pin. Table 3.5.1 shows data assignment to the output port bits on the memory map.

At initial reset, R00–R03 and R10–R13 are set to 1 and R20 to 0, is shown in the Table 3.5.1.

Table 3.5.1 I/O Memory Map

| Address |      | Regi | ister |     |      |      |      |             | Comment                         |

|---------|------|------|-------|-----|------|------|------|-------------|---------------------------------|

| Addicoo | D3   | D2   | D1    | D0  | Name | Init | 1    | 0           | Comment                         |

|         | R03  | R02  | R01   | R00 | R03  | 1    | High | Low         | Output port                     |

| 0FCH    |      | R/   | W     |     | R02  | 1    | High | Low         | Output port                     |

| UPCH    |      |      |       |     | R01  | 1    | High | Low         | Output port                     |

|         |      |      |       |     | R00  | 1    | High | Low         | Output port                     |

|         | R13  | R12  | R11   | R10 | R13  | 1    | High | Low         | Output port                     |

| 0FDH    |      | R/   | W     |     | R12  | 1    | High | Low         | Output port                     |

| OFDIT   |      |      |       |     | R11  | 1    | High | Low         | Output port                     |

|         |      |      |       |     | R10  | 1    | High | Low         | Output port                     |

|         | OPDT | OPON | IOC   | R20 | OPDT | -    | High | Low         | Analog comparator data (0 or 1) |

| 0FFH    | R    |      | R/W   |     | OPON | 0    | On   | Off         | Analog comparator on/off        |

| UFFH    |      |      |       |     | IOC  | 0    | Out  | ln          | I/O port control out/in         |

|         |      |      |       | R20 | 0    | High | Low  | Output port |                                 |

Note: Init = value at initial reset, - = not set on the circuit

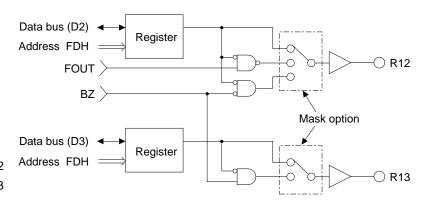

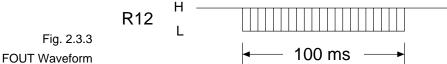

# R12 and R13 (FOUT, BZ, $\overline{BZ}$ )

Among the output ports, R12 and R13 each have mask options (normally, DC output) as listed in Table 3.5.2.

Table 3.5.2 R12 and R13 Mask Options

| Pin | Mask options                                                               |

|-----|----------------------------------------------------------------------------|

| R12 | DC, FOUT, $\overline{BZ}$ ( $\overline{fosc1/8}$ , $\overline{fosc1/16}$ ) |

| R13 | DC, BZ (fosc1/8, fosc1/16)                                                 |

FOUT (frequency output divided OSC1 clock) becomes valid when 0 is written into the register, and appears a high-level DC output when 1 is written into the register (see Figure 3.5.2 at R12 pin).

BZ (buzzer) and  $\overline{BZ}$  become valid when 0 is written into the register, and appear a low-level DC output when 1 is written into the register (see Figure 3.5.2 at R-port pins).

Fig. 3.5.2 Configuration of R12 and R13

Note It is possible that hazard appear when the FOUT, BZ or  $\overline{BZ}$  output turns ON or OFF.

With FOUT selected, the pin provides the OSC1 oscillation clock (fosc1) or an OSC1 clock divided by 2 to 128 (selected by using mask option).

With BZ selected, the pin provides fOSC1 divided by 8 or 16 for driving a piezo-electric buzzer. A division ratio (8 or 16) can be selected by using the mask option i.e. when fOSC1 = 32 kHz, either 4 kHz or 2 kHz can be selected as fBZ.

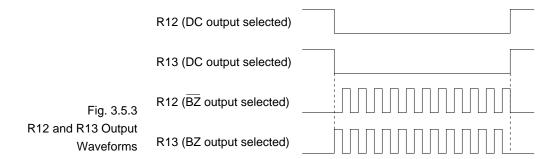

$\overline{BZ}$  is the complementary output of BZ as shown in Figure 3.5.3. If BZ alone cannot develop an effective voltage high enough to drive the buzzer,  $\overline{BZ}$  is used with BZ to double the effective voltage.

The  $\overline{BZ}$  output can be used only when the BZ output is selected at port R13.

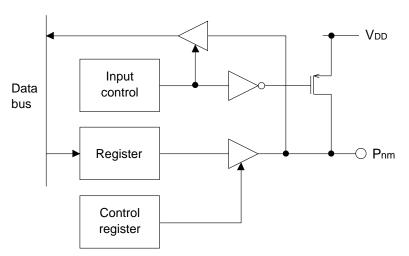

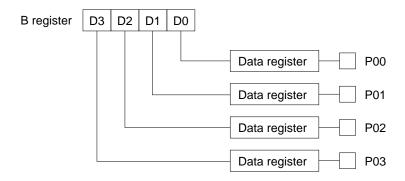

## 3.6 I/O Ports (P00-P03)

The S1C621A0 has a single 4-bit general-purpose I/O port. As shown in Figure 3.6.1, the Pnm pin works as an output port and it goes high or low levels when the value of the control register (IOC) is 1. The Pnm pin works as an input port and it goes to high-impedance state when the value of the control register is 0. (in this case, however, the Pnm pin is pulled up during and input operation under program control.)

At initial reset, the control register is set to 0 and the I/O port works as input.

Table 3.6.1 shows data assignment to the I/O port bits and the I/O control register on the memory map.

Fig. 3.6.1 I/O Port Configuration

## **Output data**

The I/O port works as an output port when the control register is set to 1. The data at address 0FEH on the data memory is output to pins P00–P03.

Note When the data at address OFEH is read with the I/O port in the output mode, the data at the pin is directly loaded to the data bus. Note that, with the Pnm pin connected to a low-impedance load, the data stored in the data memory may differ from the data that is read.

Table 3.6.1 I/O Memory Map

| Address    |       | Reg  | ister |     |      |      |      |     | Comment                                           |

|------------|-------|------|-------|-----|------|------|------|-----|---------------------------------------------------|

| / ldul C33 | D3    | D2   | D1    | D0  | Name | Init | 1    | 0   | Comment                                           |

|            | P03   | P02  | P01   | P00 | P03  | 1    | High | Low | I/O port (used as input port after initial reset) |

| OFEH       | R/W   |      |       |     | P02  | 1    | High | Low | I/O port (used as input port after initial reset) |

| UFER       |       |      |       |     | P01  | 1    | High | Low | I/O port (used as input port after initial reset) |

|            |       |      |       |     | P00  | 1    | High | Low | I/O port (used as input port after initial reset) |

|            | OPDT  | OPON | IOC   | R20 | OPDT | -    | High | Low | Analog comparator data (0 or 1)                   |

| OFFH       | R R/W |      |       |     | OPON | 0    | On   | Off | Analog comparator on/off                          |

|            |       |      |       |     | IOC  | 0    | Out  | In  | I/O port control out/in                           |

|            |       |      |       |     | R20  | 0    | High | Low | Output port                                       |

Note: Init = value at initial reset, - = not set on the circuit

#### Input data

Independently of the value of the I/O control register, the I/O port reads the value of the Pnm pin as data. Only during the read operation, the Pnm pin is pulled up (see Figure 3.6.1). This means that, in the input mode, the I/O port reads the data given to the Pnm pin and, in the output mode, reads the data loaded from the Pnm register to the Pnm pin.

# I/O control (IOC) register

A register (named IOC) which controls the output state of the I/O port (Pnm) on a 4-bit basis is assigned to 0FFH, D1 on the memory map. With 1 set in this register, the I/O port (Pnm) works as output. With 0 set in the register, the I/O port is a high-impedance state and can accept external data, and pulled up only on reading operation. At initial reset, the IOC register is set to 0.

# Notes on operation with pull-up resistors

With the Pnm pin used as input and the on-chip pull-up resistor connected to it, an input error will result if the time constant of the input line capacitive load and the on-chip pull-up resistor is greater than the read time. Although the pull-up time equals 1.5 times the wavelength of the system clock, it is necessary to limit the potential at the pin to within 0.5 times the wavelength. If this condition cannot be satisfied, an externally connected pull-up resistor must be used or the read operation repeated as many times as necessary.

# 3.7 LCD Driver (COM0-COM3, SEG0-SEG31)

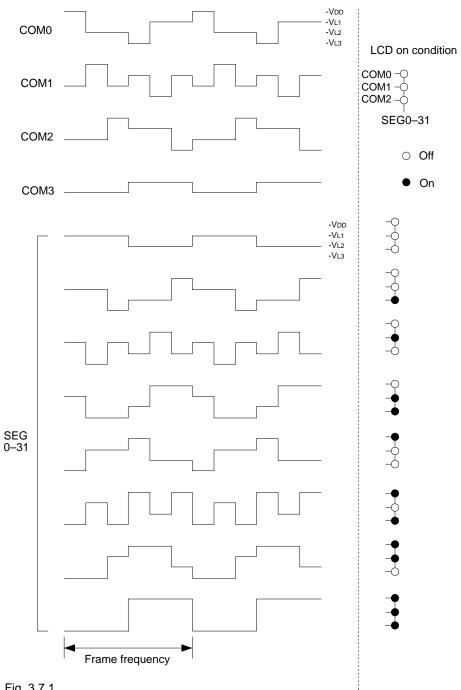

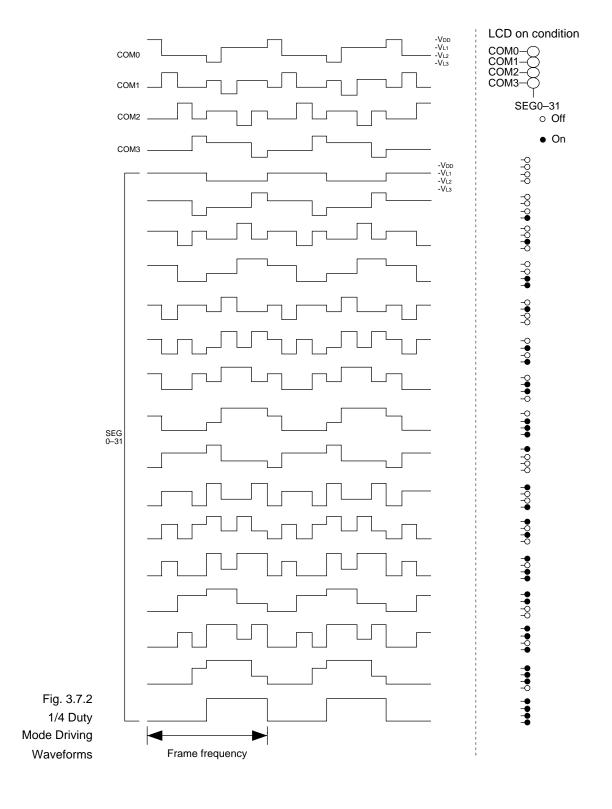

The S1C621A0 has four common pins and 32 segment pins, which can drive a maximum of 128 ( $32 \times 4$ ) segments LCD. The LCD driving power is generated on-chip and need not be supplied by an external source (see section 3.2 "Power Supply"). The LCDs are dynamically driven with a 1/4 duty using four voltages (VDD, VL1, VL2 and VL3). (A 1/3 duty can also be used by using mask option.) The frame frequency is 1/512 times the OSC1 oscillation frequency in the 1/4 duty mode, and 1/384 times in the 1/3 duty mode. Table 3.7.1 shows the differences LCD driving mode options. Figures 3.7.1 and 3.7.2 show 1/3 and 1/4 duty mode driving waveforms.

Table 3.7.1 LCD Drive Mode Options

| D | uty | COM pins used | Max. number of segments | Frame frequency | When fosc1 = 32 kHz |

|---|-----|---------------|-------------------------|-----------------|---------------------|

| 1 | 1/4 | COM0-COM3     | 128 (32 × 4)            | fosc1 / 512     | 64 Hz               |

| 1 | 1/3 | COM0-COM2     | 96 (32 × 3)             | fosc1 / 384     | 85 Hz               |

Fig. 3.7.1 1/3 Duty Mode Driving Waveforms

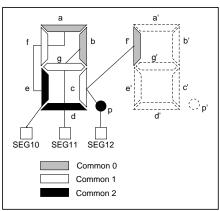

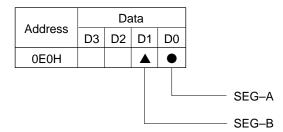

# Segment assignment

Segment data is programmed at the display memory (writeonly) addresses from 0D0H to 0EFH on the memory map. Writing 1 to the display memory turns on the associated LCD segment, and writing 0 turns off the associated LCD segment.

Any address and data and data bit can be assigned to a segment pin (SEG0–SEG31) by using mask option as long as they are written to within the above memory space. This allows design of a very flexible LCD panel. Figure 3.7.3 shows the relation between LCD segments and memory for 1/3 duty operation, for example.

| Address |    | Data |    |    |  |  |  |  |  |  |

|---------|----|------|----|----|--|--|--|--|--|--|

| Address | D3 | D2   | D1 | D0 |  |  |  |  |  |  |

| 0ECH    | d  | с    | b  | a  |  |  |  |  |  |  |

| 0EDH    | p  | g    | f  | e  |  |  |  |  |  |  |

| 0EEH    | d' | c'   | b' | a' |  |  |  |  |  |  |

| 0EFH    | p' | g'   | f' | e' |  |  |  |  |  |  |

Display memory assignment table

|   |       | Common 0 | Common 1 | Common 2 |

|---|-------|----------|----------|----------|

|   | SEG10 | EC, D0   | ED, D1   | ED, D0   |

|   |       | (a)      | (f)      | (e)      |

| • | SEG11 | EC, D1   | ED, D2   | EC, D3   |

|   |       | (b)      | (g)      | (d)      |

|   | SEG12 | EF, D1   | EC, D2   | ED, D3   |

|   |       | (f')     | (c)      | (p)      |

Pin assignment table

Fig. 3.7.3

Segment Assignment

— LCD Panel Example

The segment pins (SEG0–SEG31) can be DC output in units of two segment pins (binary output of VDD and VSS) by using the mask option. The output data corresponds to the common 0 of each segment pin.

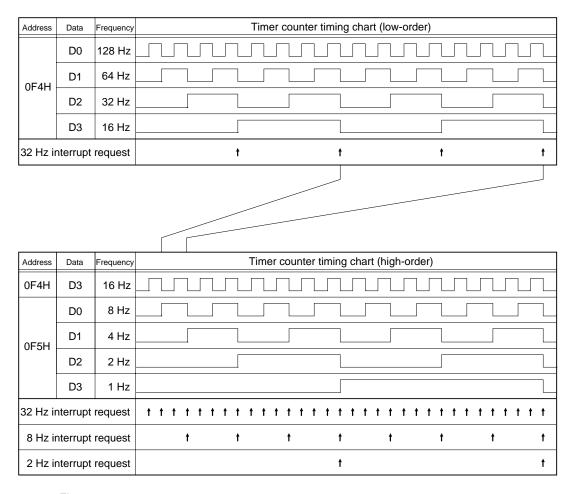

## 3.8 Timer

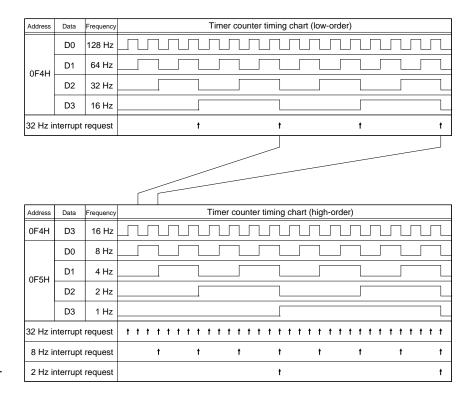

The S1C621A0 has a built-in timer using the OSC1 clock as its source oscillation frequency. The timer can be controlled by the data memory at addresses from 0F3H to 0F5H.

The information given in this section is based on foSC1 = 32.768 kHz. For a system which uses an oscillator having any other frequency at OSC1, substitute the appropriate value for 32.768 kHz throughout this section.

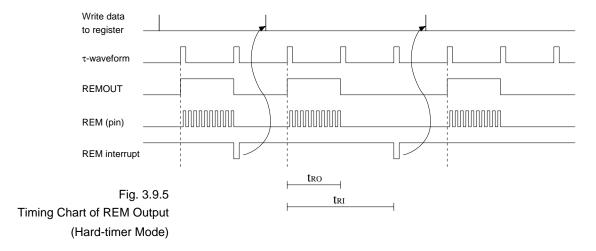

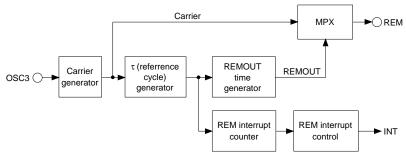

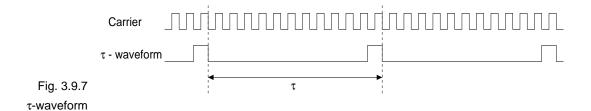

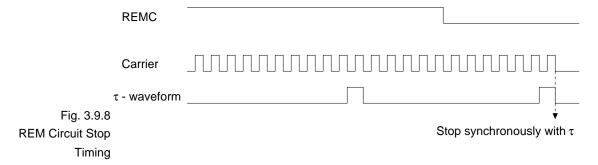

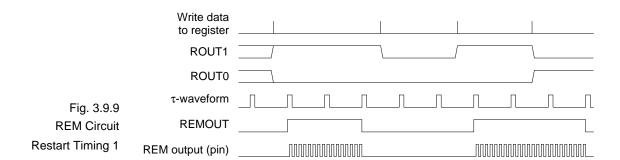

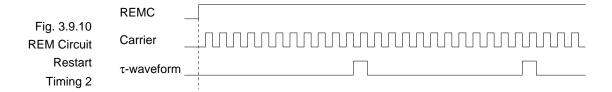

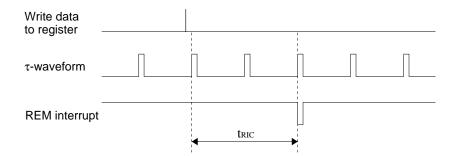

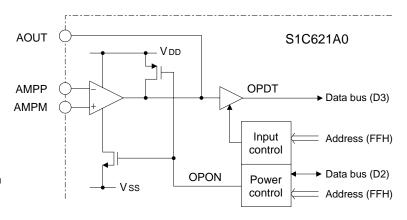

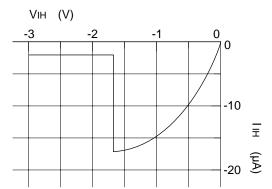

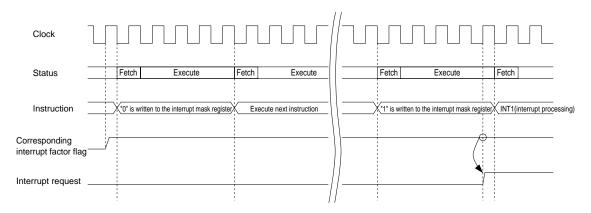

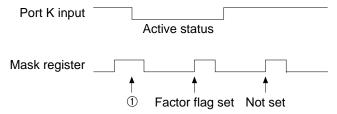

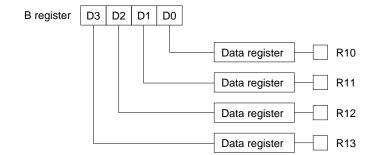

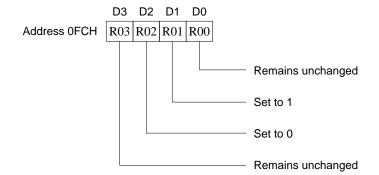

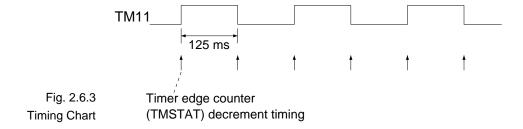

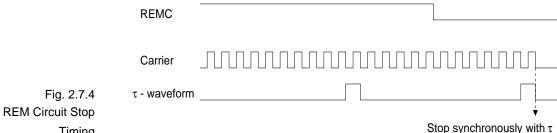

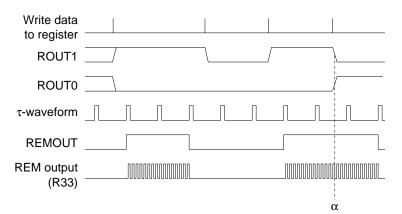

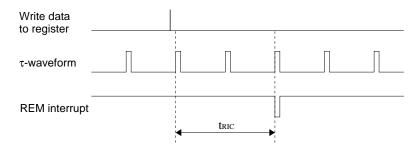

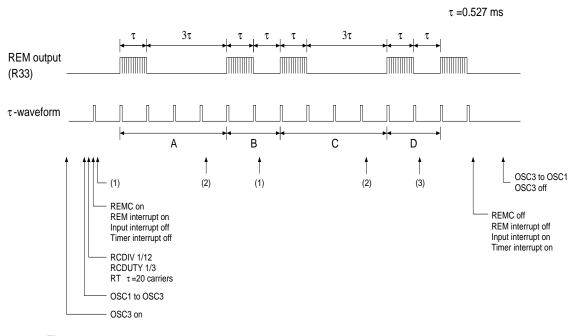

## Timer memory map